邏輯門電路

邏輯門電路概述

邏輯門電路

邏輯門電路邏輯門電路按其集成度又可分為:SSI(小規模積體電路,每片組件包含10~20個等效門)。MAI(中規模積體電路,每個組件包含20~100個等效門)。LAI(大規模積體電路,每組件內含100~1000個等效門)。VLSI(超大規模積體電路,每片組件內含1000個以上等效門)。常用的MOS門電路有NMOS,PMOS,CMOS,LDMOS,VDMOS等5種。用N溝通增強型場效應管構成的邏輯電路稱為NMOS電路;用P溝通場效應管構成的邏輯電路稱為PMOS電路;CMOS電路則是NMOS和PMOS的互補型電路,用橫向雙擴散MOS管構成的邏輯電路稱為LDMOS電路;用垂直雙擴散MOS管構成二邏輯電路稱為VDMOS電路。

門電路使用注意事項:1、電源要求:電源電壓有兩個電壓:額定電源電壓和極限電源電壓,額定電源電壓指正常工作時電源電壓的允許大小:TTL電路為5V±5%(54系列5V±10%);CMOS電路為3~15V(4000B系列3~18V)。極限工作電源電壓指超過該電源電壓器件將永久損壞。TTL電路為7V;4000系列CMOS電路為18V。2、輸入電壓要求:輸入高電平電壓應大於VIHmin而小於電源電壓;輸入低電平電壓應大於0V而小於VILmax。輸入電壓小於0V或大於電源電壓將有可能損壞邏輯電路。

邏輯門電路

邏輯門電路CMOS門電路

邏輯門電路

邏輯門電路MOS門電路:由單極型MOS管構成的門電路稱為Mos門電路。MOS電路具有製造工藝簡單、功耗低、集成度高、電源電壓使用範圍寬、抗干擾能力強等優點,特別適用於大規模積體電路。MOS門電路按所用MOS管的不同可分為三種類型:第一種是由PMOS管構成的PMOS門電路,其工作速度較低;第二種是由NMOS管構成的NMOS門電路,工作速度比PMOS電路要高,但比不上TTL電路;第三種是由PMOS管和NMOS管兩種管子共同組成的互補型電路,稱為CMOS電路,CMOS電路的優點突出,其靜態功耗極低,抗干擾能力強,工作穩定可靠且開關速度也大大高於NMOS和PMOS電路,故得到了廣泛套用。

MOS管主要參數:

1、開啟電壓VT

·開啟電壓(又稱閾值電壓):使得源極S和漏極D之間開始形成導電溝道所需的柵極電壓;

·標準的N溝道MOS管,VT約為3~6V;

·通過工藝上的改進,可以使MOS管的VT值降到2~3V。

2、直流輸入電阻RGS

·即在柵源極之間加的電壓與柵極電流之比

·這一特性有時以流過柵極的柵流表示

·MOS管的RGS可以很容易地超過1010Ω。

3、漏源擊穿電壓BVDS

·在VGS=0(增強型)的條件下,在增加漏源電壓過程中使ID開始劇增時的VDS稱為漏源擊穿電壓BVDS

·ID劇增的原因有下列兩個方面:(1)漏極附近耗盡層的雪崩擊穿,(2)漏源極間的穿通擊穿。

·有些MOS管中,其溝道長度較短,不斷增加VDS會使漏區的耗盡層一直擴展到源區,使溝道長度為零,即產生漏源間的穿通,穿通後,源區中的多數載流子,將直接受耗盡層電場的吸引,到達漏區,產生大的ID

4、柵源擊穿電壓BVGS

·在增加柵源電壓過程中,使柵極電流IG由零開始劇增時的VGS,稱為柵源擊穿電壓BVGS。

5、低頻跨導gm

·在VDS為某一固定數值的條件下,漏極電流的微變數和引起這個變化的柵源電壓微變數之比稱為跨導

·gm反映了柵源電壓對漏極電流的控制能力

·是表征MOS管放大能力的一個重要參數

·一般在十分之幾至幾mA/V的範圍內

6、導通電阻RON

·導通電阻RON說明了VDS對ID的影響,是漏極特性某一點切線的斜率的倒數

·在飽和區,ID幾乎不隨VDS改變,RON的數值很大,一般在幾十千歐到幾百千歐之間

·由於在數字電路中,MOS管導通時經常工作在VDS=0的狀態下,所以這時的導通電阻RON可用原點的RON來近似

·對一般的MOS管而言,RON的數值在幾百歐以內

7、極間電容

·三個電極之間都存在著極間電容:柵源電容CGS、柵漏電容CGD和漏源電容CDS

·CGS和CGD約為1~3pF

·CDS約在0.1~1pF之間

8、低頻噪聲係數NF

·噪聲是由管子內部載流子運動的不規則性所引起的

·由於它的存在,就使一個放大器即便在沒有信號輸人時,在輸出端也出現不規則的電壓或電流變化

·噪聲性能的大小通常用噪聲係數NF來表示,它的單位為分貝(dB)

·這個數值越小,代表管子所產生的噪聲越小

·低頻噪聲係數是在低頻範圍內測出的噪聲係數

·場效應管的噪聲係數約為幾個分貝,它比雙極性三極體的要小

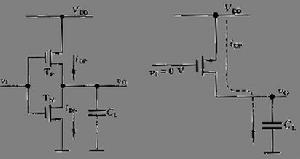

邏輯門電路CMOS反相器

邏輯門電路CMOS反相器CMOS反相器:CMOS邏輯門電路是在TTL電路問世之後,所開發出的第二種廣泛套用的數字集成器件,從發展趨勢來看,由於製造工藝的改進,CMOS電路的性能有可能超越TTL而成為占主導地位的邏輯器件。CMOS電路的工作速度可與TTL相比較,而它的功耗和抗干擾能力則遠優於TTL。此外,幾乎所有的超大規模存儲器件,以及PLD器件都採用CMOS藝製造,且費用較低。早期生產的CMOS門電路為4000系列,隨後發展為4000B系列。當前與TTL兼容的CMO器件如74HCT系列等可與TTL器件交換使用。

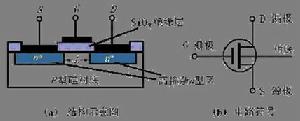

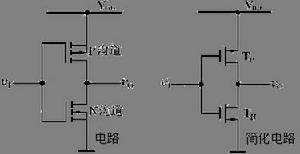

MOSFET有P溝道和N溝道兩種,每種中又有耗盡型和增強型兩類。由N溝道和P溝道兩種MOSFET組成的電路稱為互補MOS或CMOS電路。CMOS反相器電路,由兩隻增強型MOSFET組成,其中一個為N溝道結構,另一個為P溝道結構。為了電路能正常工作,要求電源電壓VDD大於兩個管子的開啟電壓的絕對值之和,即VDD>(VTN+|VTP|)。

邏輯門電路工作原理

邏輯門電路工作原理 邏輯門電路傳輸特性

邏輯門電路傳輸特性 邏輯門電路工作速度

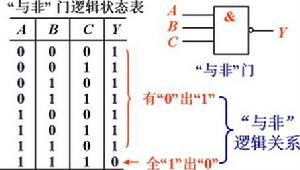

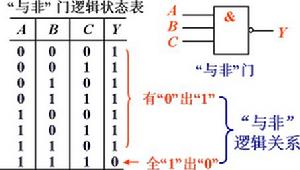

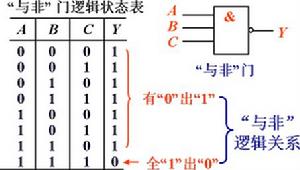

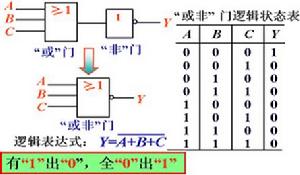

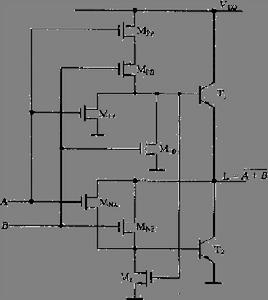

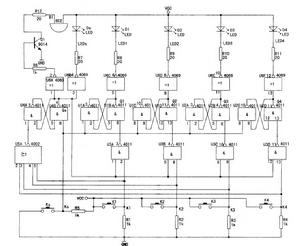

邏輯門電路工作速度【CMOS門電路】1、與非門電路:包括兩個串聯的N溝道增強型MOS管和兩個並聯的P溝道增強型MOS管。每個輸入端連到一個N溝道和一個P溝道MOS管的柵極。當輸入端A、B中只要有一個為低電平時,就會使與它相連的NMOS管截止,與它相連的PMOS管導通,輸出為高電平;僅當A、B全為高電平時,才會使兩個串聯的NMOS管都導通,使兩個並聯的PMOS管都截止,輸出為低電平。因此,這種電路具有與非的邏輯功能,即n個輸入端的與非門必須有n個NMOS管串聯和n個PMOS管並聯。

邏輯門電路

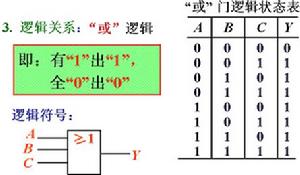

邏輯門電路3、異或門電路:它由一級或非門和一級與或非門組成。或非門的輸出。而與或非門的輸出L即為輸入A、B的異或如在異或門的後面增加一級反相器就構成異或非門,由於具有的功能,因而稱為同或門。

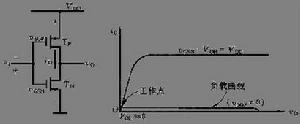

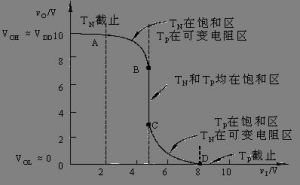

【CMOS傳輸門】MOSFET的輸出特性在原點附近呈線性對稱關係,因而它們常用作模擬開關。模擬開關廣泛地用於取樣——保持電路、斬波電路、模數和數模轉換電路等。下面著重介紹CMOS傳輸門。所謂傳輸門(TG)就是一種傳輸模擬信號的模擬開關。CMOS傳輸門由一個P溝道和一個N溝道增強型MOSFET並聯而成,如上圖所示。TP和TN是結構對稱的器件,它們的漏極和源極是可互換的。設它們的開啟電壓|VT|=2V且輸入模擬信號的變化範圍為-5V到+5V。為使襯底與漏源極之間的PN結任何時刻都不致正偏,故TP的襯底接+5V電壓,而TN的襯底接-5V電壓。兩管的柵極由互補的信號電壓(+5V和-5V)來控制,分別用C和表示。

傳輸門的工作情況如下:當C端接低電壓-5V時TN的柵壓即為-5V,vI取-5V到+5V範圍內的任意值時,TN均不導通。同時、TP的柵壓為+5V,TP亦不導通。可見,當C端接低電壓時,開關是斷開的。為使開關接通,可將C端接高電壓+5V。此時TN的柵壓為+5V,vI在-5V到+3V的範圍內,TN導通。同時TP的棚壓為-5V,vI在-3V到+5V的範圍內TP將導通。由上分析可知,當vI<-3V時,僅有TN導通,而當vI>+3V時,僅有TP導通當vI在-3V到+3V的範圍內,TN和TP兩管均導通。進一步分析還可看到,一管導通的程度愈深,另一管的導通程度則相應地減小。換句話說,當一管的導通電阻減小,則另一管的導通電阻就增加。由於兩管系並聯運行,可近似地認為開關的導通電阻近似為一常數。這是CMOS傳輸出門的優點。在正常工作時,模擬開關的導通電阻值約為數百歐,當它與輸入阻抗為兆歐級的運放串接時,可以忽略不計。CMOS傳輸門除了作為傳輸模擬信號的開關之外,也可作為各種邏輯電路的基本單元電路。

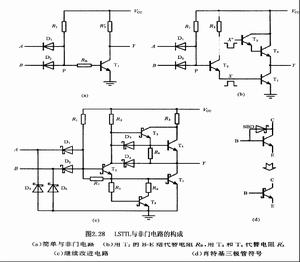

雙極型門電路

邏輯門電路

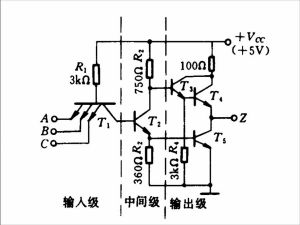

邏輯門電路LSTTL與非門電路:該電路可以看作由二極體D1、D2構成的與門、三極體T2構成的非門及用三極體T3、T4取代R3′,T2的BE結取代RB的改進型與非門的組合。1、LSTTL門電路的靜態特性:(1)LSTTL門電路的靜態輸入特性、(2)LSTTL門電路的靜態輸出特性、LSTTL電路中的74LS125晶片有如圖所示三態輸出方式:0、1和高電阻。三態電路特別適合於匯流排結構系統和外圍電路,也適用於數字控制設備,數字儀表中一般邏輯電路間的連線。(3)LSTTL門電路的電壓傳輸特性、(4)LSTTL門電路的抗干擾特性――噪聲容限UNLSTTL門電路的輸入低電平噪聲容限VNL=0.3V,輸入高電平噪聲容限VNH=0.5V。2、LSTTL門電路的動態特性:(1)LSTTL門電路的平均傳輸延遲時間TP,由於二極體和三極體由導通到截止或者由截止到導通都需要時間,且受到電路中的寄生電容和負載電容等的影響,電路的輸出波形總是滯後於輸入波形。(2)LSTTL門電路的動態尖峰電流,在電源電流脈衝的邊沿(主要是下降沿)產生了尖峰,這就是動態尖峰電流。

3、LSTTL門電路的溫度特性:溫度變化對LSTTL門電路電氣性能的影響比對CMOS門電路影響大得多,主要是:

1、輸入高電平通過圖2.30中D1、D2的漏電流I1H隨溫度升高而增大。OC門輸出高電平或輸出高電阻狀態的漏電流IOZ會增大,電路的輸出驅動能力將下降。2、輸出高電平VOHP隨溫度降低而降低。其原因是VOH=VCC-2VBE,溫度降低導致VBE增大,故VOH減小。根據噪聲容限的概念,VOH的減小則系統的抗干擾能力降低。3、LSTTL門電路的閾值電壓VT主要取決於VD和VBE1,於是VT隨著溫度的升高而下降。因溫度每升高1℃,則PN結壓降低減小2mV,所以當溫度從-55℃上升到+125℃時,VT將下降300mV以上。

邏輯門電路

邏輯門電路1、普通TTL門電路:①將LSTTL門電路74ls00中的肖特基三極體換成普通三極體,將肖特基二極體換成普通二極體,將輸入端的二極體與門換成多射極電晶體輸與門,普通TTL與非門電路。②三3輸入與非門7410的工作狀態表。2、ECL門電路(1)“發射極耦合邏輯”門電路,簡稱為ECL門電路,是一種非飽和型的高速邏輯電路。(2)ECL或/或非門的電壓傳輸特性。(3)ECL電路與TTL電路相比較優點主要表現在:①由於輸出端採用射極輸出結構,故輸出電阻很低,帶負載能很強。例如國產CE10K系列門電路能驅動同類門電路數目達90個以上。②工作速度最快。③ECL電路可以直接將輸出端並聯以實現“線或”的邏輯功能,同時有、互補的輸出端,使用非常方便。④由於T1~T5管的ic幾乎相等,故電路開關過程中電源電流幾乎沒有變化,電路內部的開關噪聲很小。缺點主要表現在:①功耗大。②抗干擾能力差,即噪聲容限低,因為ECL電路的邏輯擺幅僅0.8V,直流噪聲容限僅200mV左右。③輸出電平的穩定性較差。

3、I2L電路:(1)集成注入邏輯”門電路,簡稱I2L電路,它具有結構簡單,功耗低的優點,特別適合製成大規模積體電路。(2)I2L電路的多集電極輸出結構在構成複雜邏輯電路時十分方便。(3)I2L門電路與TTL門電路的比較

I2L電路的優點主要表現在:①I2L電路能在低電壓、微電流下工作。②I2L門電路結構簡單。③各邏輯單元之間不需要隔離。I2L電路的缺點主要表現在:①開關速度慢。②抗干擾能力差。

BicMOS門電路

雙極型CMOS或BiCMOS的特點在於,利用了雙極型器件的速度快和MOSFET的功耗低兩方面的優勢,因而這種邏輯門電路受到用戶的重視。

邏輯門電路

邏輯門電路 邏輯門電路

邏輯門電路套用舉例

在使用CMOS電路時必須採用以下安全措施:1、存放CMOS積體電路時要禁止,一般放在金屬容器中,或用導電材料將引腳短路,不要放在易產生靜電高壓的化工材料或化纖織物中。2、焊接CMOS電路時,一般用20W內熱式電烙鐵,而且烙鐵要有良好的接地線;也可以用電烙鐵斷電後的餘熱快速焊接;禁止在電路通電情況下焊接。3、為了防止輸入端保護二極體反向擊穿,輸入電壓必須處在VDD和Vss之間,即Vdd≥VI≥Vss。4、測試CMOS電路時,如果信號電源和電路供電採用2組電源,則在開機時應先接通電路供電電源,後開信號電源。關機時,應先關信號電源,後關電路供電電源,即在CMOS電路本身沒有接通供電電源的情況下,不允許輸入端的信號輸入。

5、多餘輸入端絕對不能懸空,否則容易接受外界干擾,破壞了正常的邏輯關係,甚至損壞。對於與門、與非門的多餘輸入端應接Vdd或高電平或與使用的輸入端並聯。對於或門、或非門多餘的輸入端應接地或低電平或與使用的輸入端並聯。6、必須在其他元器件在印製電路板上安裝就緒後,再裝CMOS電路,避免CMOS電路輸入端懸空。CMOS電路從印製電路板上拔出時,務必先切斷印製板上的電源。7、輸入端連線較長時,由於分布電容和分布電感的影響,容易構成LC振盪或損壞保護二極體,必須在輸入端串聯1個10~20ΚΩ的電阻R。8、防止CMOS電路輸入端噪聲干擾的方法是:在前一級和CMOS電路之間接入施密特觸發器整形電路,或加入濾波電容濾掉噪聲。

使用TTL電路應注意的問題如下:1、TTL電路的電源均採用+5V,使用時,不能將電源與地顛倒接錯,也不能接高於5.5V的電源。否則會損壞器件。2、電路的輸入端不能直接與高於+5.5V或低於-0.5V的低內阻電源連線,因為低內阻電源供給較大電流而燒壞器件。3、輸出端不允許與電源或地短接,必須通過電阻與電源連線,以提高輸出電平。4、插入或拔出積體電路時,務必切斷電源,否則會因電源衝擊而造成永久損壞。5、多餘輸入端不允許懸空。接地電阻的阻值要求R≤=500。

邏輯門電路

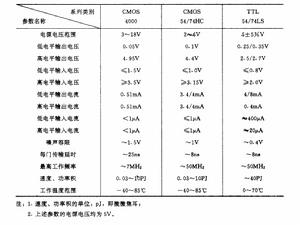

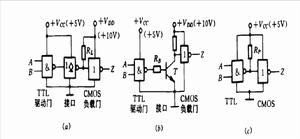

邏輯門電路TTL、CMOS接口電路所謂“接口電路”,就是用於不同類型邏輯門電路之間或邏輯門電路與外部電路之間,使二者有效連線,正常工作的中間電路。常用數字積體電路技術參數比較如下表:

1、CMOS電路驅動TTL電路:用CMOS電路去驅動TTL電路時,需要解決的問題是CMOS電路不能提供足夠大的驅動電流。CMOS電路允許的最大灌電流一般只有0.4mA左右,而TTL電路的輸入短路電流Iis約為1.4mA。

邏輯門電路

邏輯門電路 邏輯門電路搶答器

邏輯門電路搶答器利用“與非”門設計製作燈頭“聲光控節能開關”:聲光控節能開關白天或光線較強的場合即使有較大的聲響,也能控制燈泡不亮,晚上或光線較暗時,遇到聲響(比如腳步聲、說話聲等)後,燈自動點亮,經過設定的時間後自動熄滅。適用於樓梯,走廊等只需短時間照明的地方。

參考文獻

1、http://www.fjtu.com.cn/fjnu/courseware/0321/course/_source/web/lesson/char2/j6.htm#j2

2、http://www.eyw.edu.cn/zhuanti/jpkc/dgjs/mysite/content/ch7/7.3.htm

3、http://www.studyemc.net/simple/index.php?t3231.html

電路基礎

| 電的發明是人類工業發展的開始;有了電世界才有今天的科技發達;社會繁榮! |