綜述

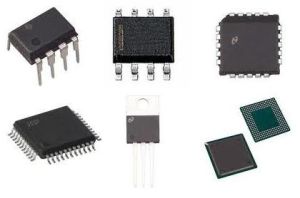

IC積體電路

IC積體電路 為什麼會產生積體電路?我們知道任何發明創造背後都是有驅動力的,而驅動力往往來源於問題。那么積體電路產生之前的問題是什麼呢?我們看一下1942年在美國誕生的世界上第一台電子計算機,它是一個占地150平方米、重達30噸的龐然大物,裡面的電路使用了17468隻電子管、7200隻電阻、10000隻電容、50萬條線,耗電量150千瓦。顯然,占用面積大、無法移動是它最直觀和突出的問題;如果能把這些電子元件和連線集成在一小塊載體上該有多好!我們相信,有很多人思考過這個問題,也提出過各種想法。典型的如英國雷達研究所的科學家達默,他在1952年的一次會議上提出:可以把電子線路中的分立元器件,集中製作在一塊半導體晶片上,一小塊晶片就是一個完整電路,這樣一來,電子線路的體積就可大大縮小,可靠性大幅提高。這就是初期積體電路的構想,電晶體的發明使這種想法成為了可能,1947年在美國貝爾實驗室製造出來了第一個電晶體,而在此之前要實現電流放大功能只能依靠體積大、耗電量大、結構脆弱的電子管。電晶體具有電子管的主要功能,並且克服了電子管的上述缺點,因此在電晶體發明後,很快就出現了基於半導體的積體電路的構想,也就很快發明出來了積體電路。傑克·基爾比(Jack Kilby)和羅伯特·諾伊斯(Robert Noyce)在1958~1959期間分別發明了鍺積體電路和矽積體電路。

講完了歷史,我們再來看現狀。積體電路已經在各行各業中發揮著非常重要的作用,是現代信息社會的基石。積體電路的含義,已經遠遠超過了其剛誕生時的定義範圍,但其最核心的部分,仍然沒有改變,那就是“集成”,其所衍生出來的各種學科,大都是圍繞著“集成什麼”、“如何集成”、“如何處理集成帶來的利弊”這三個問題來開展的。矽積體電路是主流,就是把實現某種功能的電路所需的各種元件都放在一塊矽片上,所形成的整體被稱作積體電路。對於“集成”,想像一下我們住過的房子可能比較容易理解:很多人小時候都住過農村的房子,那時房屋的主體也許就是三兩間平房,發揮著臥室的功能,門口的小院子擺上一副桌椅,就充當客廳,旁邊還有個炊煙裊裊的小矮屋,那是廚房,而具有獨特功能的廁所,需要有一定的隔離,有可能在房屋的背後,要走上十幾米。後來,到了城市裡,或者鄉村城鎮化,大家都住進了樓房或者套房,一套房裡面,有客廳、臥室、廚房、衛生間、陽台,也許只有幾十平方米,卻具有了原來占地幾百平方米的農村房屋的各種功能,這就是集成。

當然現如今的積體電路,其集成度遠非一套房能比擬的,或許用一幢摩登大樓可以更好地類比:地面上有商鋪、辦公、食堂、酒店式公寓,地下有幾層是停車場,停車場下面還有地基——這是積體電路的布局,模擬電路和數字電路分開,處理小信號的敏感電路與翻轉頻繁的控制邏輯分開,電源單獨放在一角。每層樓的房間布局不一樣,走廊也不一樣,有回字形的、工字形的、幾字形的——這是積體電路器件設計,低噪聲電路中可以用摺疊形狀或“叉指”結構的電晶體來減小結面積和柵電阻。各樓層直接有高速電梯可達,為了效率和功能隔離,還可能有多部電梯,每部電梯能到的樓層不同——這是積體電路的布線,電源線、地線單獨走線,負載大的線也寬;時鐘與信號分開;每層之間布線垂直避免干擾;CPU與存儲之間的高速匯流排,相當於電梯,各層之間的通孔相當於電梯間。

特點

積體電路

積體電路 積體電路或稱微電路(microcircuit)、 微晶片(microchip)、晶片(chip)在電子學中是一種把電路(主要包括半導體裝置,也包括被動元件等)小型化的方式,並通常製造在半導體晶圓表面上。

前述將電路製造在半導體晶片表面上的積體電路又稱薄膜(thin-film)積體電路。另有一種厚膜(thick-film)混成積體電路(hybrid integrated circuit)是由獨立半導體設備和被動元件,集成到襯底或線路板所構成的小型化電路。

本文是關於單片(monolithic)積體電路,即薄膜積體電路。

積體電路具有體積小,重量輕,引出線和焊接點少,壽命長,可靠性高,性能好等優點,同時成本低,便於大規模生產。它不僅在工、民用電子設備如收錄機、電視機、計算機等方面得到廣泛的套用,同時在軍事、通訊、遙控等方面也得到廣泛的套用。用積體電路來裝配電子設備,其裝配密度比電晶體可提高几十倍至幾千倍,設備的穩定工作時間也可大大提高。

分類

功能結構

積體電路

積體電路 模擬積體電路又稱線性電路,用來產生、放大和處理各種模擬信號(指幅度隨時間變化的信號。例如半導體收音機的音頻信號、 錄放機的磁帶信號等),其輸入信號和輸出信號成比例關係。而數字積體電路用來產生、放大和處理各種數位訊號(指在時間上和幅度上離散取值的信號。例如3G手機、數位相機、電腦 CPU、數位電視的邏輯控制和重放的音頻信號和視頻信號)。

製作工藝

積體電路按製作工藝可分為半導體積體電路和膜集成電路。

膜積體電路又分類厚膜積體電路和薄膜積體電路。

集成度高低

積體電路按集成度高低的不同可分為:

SSIC 小規模積體電路(Small Scale Integrated circuits)

MSIC 中規模積體電路(Medium Scale Integrated circuits)

LSIC 大規模積體電路(Large Scale Integrated circuits)

VLSIC 超大規模積體電路(Very Large Scale Integrated circuits)

ULSIC特大規模積體電路(Ultra Large Scale Integrated circuits)

GSIC 巨大規模積體電路也被稱作極大規模積體電路或超特大規模積體電路(Giga Scale Integration)。

導電類型

積體電路

積體電路 雙極型積體電路的製作工藝複雜,功耗較大,代表積體電路有TTL、ECL、HTL、LST-TL、STTL等類型。單極型積體電路的製作工藝簡單,功耗也較低,易於製成大規模積體電路,代表積體電路有CMOS、NMOS、PMOS等類型。

按用途

積體電路

積體電路 積體電路按用途可分為電視機用積體電路、音響用積體電路、影碟機用積體電路、錄像機用積體電路、電腦(微機)用積體電路、電子琴用積體電路、通信用積體電路、照相機用積體電路、遙控積體電路、語言積體電路、報警器用積體電路及各種專用積體電路。

1.電視機用積體電路包括行、場掃描積體電路、中放積體電路、伴音積體電路、彩色解碼積體電路、AV/TV轉換積體電路、開關電源積體電路、遙控積體電路、麗音解碼積體電路、畫中畫處理積體電路、微處理器(CPU)積體電路、存儲器積體電路等。

2.音響用積體電路包括AM/FM高中頻電路、立體聲解碼電路、音頻前置放大電路、音頻運算放大積體電路、音頻功率放大積體電路、環繞聲處理積體電路、電平驅動積體電路,電子音量控制積體電路、延時混響積體電路、電子開關積體電路等。

3.影碟機用積體電路有系統控制積體電路、視頻編碼積體電路、MPEG解碼積體電路、音頻信號處理積體電路、音響效果積體電路、RF信號處理積體電路、數位訊號處理積體電路、伺服積體電路、電動機驅動積體電路等。

4.錄像機用積體電路有系統控制積體電路、伺服積體電路、驅動積體電路、音頻處理積體電路、視頻處理積體電路。

5.計算機積體電路,包括中央控制單元(CPU)、記憶體儲器、外存儲器、I/O控制電路等。

6.通信積體電路

7.專業控制積體電路

按套用領域分

積體電路按套用領域可分為標準通用積體電路和專用積體電路。

按外形分

積體電路按外形可分為圓形(金屬外殼電晶體封裝型,一般適合用於大功率)、扁平型(穩定性好,體積小)和雙列直插型。

簡史

積體電路

積體電路 世界積體電路發展歷史

1947年:美國貝爾實驗室的約翰·巴丁、布拉頓、肖克萊三人發明了電晶體,這是微電子技術發展中第一個里程碑;

1950年:結型電晶體誕生

1950年: R Ohl和肖克萊發明了離子注入工藝

1951年:場效應電晶體發明

1956年:C S Fuller發明了擴散工藝

1958年:仙童公司Robert Noyce與德儀公司基爾比間隔數月分別發明了積體電路,開創了世界微電子學的歷史;

1960年:H H Loor和E Castellani發明了光刻工藝

1962年:美國RCA公司研製出MOS場效應電晶體

1963年:F.M.Wanlass和C.T.Sah首次提出CMOS技術,今天,95%以上的積體電路晶片都是基於CMOS工藝

1964年:Intel摩爾提出摩爾定律,預測電晶體集成度將會每18個月增加1倍

1966年:美國RCA公司研製出CMOS積體電路,並研製出第一塊門陣列(50門),為現如今的大規模積體電路發展奠定了堅實基礎,具有里程碑意義

1967年:套用材料公司(Applied Materials)成立,現已成為全球最大的半導體設備製造公司

1971年:Intel推出1kb動態隨機存儲器(DRAM),標誌著大規模積體電路出現

1971年:全球第一個微處理器4004由Intel公司推出,採用的是MOS工藝,這是一個里程碑式的發明

1974年:RCA公司推出第一個CMOS微處理器1802

1976年:16kb DRAM和4kb SRAM問世

1978年:64kb動態隨機存儲器誕生,不足0.5平方厘米的矽片上集成了14萬個電晶體,標誌著超大規模積體電路(VLSI)時代的來臨

1979年:Intel推出5MHz 8088微處理器,之後,IBM基於8088推出全球第一台PC

1981年:256kb DRAM和64kb CMOS SRAM問世

1984年:日本宣布推出1Mb DRAM和256kb SRAM

1985年:80386微處理器問世,20MHz

1988年:16M DRAM問世,1平方厘米大小的矽片上集成有3500萬個電晶體,標誌著進入超大規模積體電路(VLSI)階段

1989年:1Mb DRAM進入市場

1989年:486微處理器推出,25MHz,1μm工藝,後來50MHz晶片採用 0.8μm工藝

1992年:64M位隨機存儲器問世

1993年:66MHz奔騰處理器推出,採用0.6μm工藝

1995年:Pentium Pro, 133MHz,採用0.6-0.35μm工藝;

1997年:300MHz奔騰Ⅱ問世,採用0.25μm工藝

1999年:奔騰Ⅲ問世,450MHz,採用0.25μm工藝,後採用0.18μm工藝

2000年:1Gb RAM投放市場

2000年:奔騰4問世,1.5GHz,採用0.18μm工藝

2001年:Intel宣布2001年下半年採用0.13μm工藝。

2003年:奔騰4 E系列推出,採用90nm工藝。

2005年:intel 酷睿2系列上市,採用65nm工藝。

2007年:基於全新45納米High-K工藝的intel酷睿2 E7/E8/E9上市。

2009年:intel酷睿i系列全新推出,創紀錄採用了領先的32納米工藝,並且下一代22納米工藝正在研發。

我國積體電路發展歷史

我國積體電路產業誕生於六十年代,共經歷了三個發展階段:

1965年-1978年:以計算機和軍工配套為目標,以開發邏輯電路為主要產 品,初步建立積體電路工業基礎及相關設備、儀器、材料的配套條件

1978年-1990年:主要引進美國二手設備,改善積體電路裝備水平,在“治散治亂”的同時,以消費類整機作為配套重點,較好地解決了彩電積體電路的國產化

1990年-2000年:以908工程、909工程為重點,以CAD為突破口,抓好科技攻關和北方科研開發基地的建設,為信息產業服務,積體電路行業取得了新的發展。

積體電路產業是對積體電路產業鏈各環節市場銷售額的總體描述,它不僅僅包含集成電路市場,也包括IP核市場、EDA市場、晶片代工市場、封測市場,甚至延伸至設備、材料市場。

積體電路產業不再依賴CPU、存儲器等單一器件發展,移動互聯、三網融合、多屏互動、智慧型終端帶來了多重市場空間,商業模式不斷創新為市場注入新活力。目前我國積體電路產業已具備一定基礎,多年來我國積體電路產業所聚集的技術創新活力、市場拓展能力、資源整合動力以及廣闊的市場潛力,為產業在未來5年~10年實現快速發展、邁上新的台階奠定了基礎。

檢測常識

IC

IC 1、檢測前要了解積體電路及其相關電路的工作原理

檢查和修理積體電路前首先要熟悉所用積體電路的功能、內部電路、主要電氣參數、各引腳的作用以及引腳的正常電壓、波形與外圍元件組成電路的工作原理。

2、測試避免造成引腳間短路

電壓測量或用示波器探頭測試波形時,避免造成引腳間短路,最好在與引腳直接連通的外圍印刷電路上進行測量。任何瞬間的短路都容易損壞積體電路,尤其在測試扁平型封裝的CMOS積體電路時更要加倍小心。

3、嚴禁在無隔離變壓器的情況下,用已接地的測試設備去接觸底板帶電的電視、音響、錄像等設備

嚴禁用外殼已接地的儀器設備直接測試無電源隔離變壓器的電視、音響、錄像等設備。雖然一般的收錄機都具有電源變壓器,當接觸到較特殊的尤其是輸出功率較大或對採用的電源性質不太了解的電視或音響設備時,首先要弄清該機底盤是否帶電,否則極易與底板帶電的電視、音響等設備造成電源短路,波及積體電路,造成故障的進一步擴大。

4、要注意電烙鐵的絕緣性能

不允許帶電使用烙鐵焊接,要確認烙鐵不帶電,最好把烙鐵的外殼接地,對MOS電路更應小心,能採用6~8V的低壓電烙鐵就更安全。

5、要保證焊接質量

焊接時確實焊牢,焊錫的堆積、氣孔容易造成虛焊。焊接時間一般不超過3秒鐘,烙鐵的功率套用內熱式25W左右。已焊接好的積體電路要仔細查看,最好用歐姆表測量各引腳間有否短路,確認無焊錫粘連現象再接通電源。

6、不要輕易斷定積體電路的損壞

不要輕易地判斷積體電路已損壞。因為積體電路絕大多數為直接耦合,一旦某一電路不正常,可能會導致多處電壓變化,而這些變化不一定是積體電路損壞引起的,另外在有些情況下測得各引腳電壓與正常值相符或接近時,也不一定都能說明積體電路就是好的。因為有些軟故障不會引起直流電壓的變化。

7、測試儀表內阻要大

測量積體電路引腳直流電壓時,應選用表頭內阻大於20KΩ/V的萬用表,否則對某些引腳電壓會有較大的測量誤差。

8、要注意功率積體電路的散熱

功率積體電路應散熱良好,不允許不帶散熱器而處於大功率的狀態下工作。

9、引線要合理

如需要加接外圍元件代替積體電路內部已損壞部分,應選用小型元器件,且接線要合理以免造成不必要的寄生耦合,尤其是要處理好音頻功放積體電路和前置放大電路之間的接地端。

| 第0部分 | 第一部分 | 第二部分 | 第三部分 | 第四部分 | ||||

|---|---|---|---|---|---|---|---|---|

| 符號 | 意義 | 符合 | 意義 | 意義 | 符號 | 意義 | 符合 | 意義 |

| C | C表示 中國製造 | T | TTL電路 | 用數字表 示器件的 系列代號 | C | 0~70℃ | F | 多層陶瓷扁平 |

| H | HTL電路 | G | ‐25~70℃ | B | 塑膠扁平 | |||

| E | ECL電路 | L | ‐24~85℃ | H | 黑瓷扁平 | |||

| C | CMOS電路 | E | ‐40~85℃ | D | 多層陶瓷雙列直插 | |||

| M | 存儲器 | R | ‐55~85℃ | J | 黑瓷雙列直插 | |||

| µ | 微型機電路 | M | ‐55~125℃ | P | 塑膠雙列直插 | |||

| F | 線性放大器 | S | 塑膠單列直插 | |||||

| W | 穩定器 | K | 金屬菱形 | |||||

| B | 非線性電路 | T | 金屬圓形 | |||||

| J | 接口電路 | C | 陶瓷晶片載體 | |||||

| AD | A/D轉換器 | E | 塑膠晶片載體 | |||||

| DA | D/A轉換器 | G | 網路針柵陳列 | |||||

| D | 音響、電視電路 | |||||||

| SC | 通信專用電路 | |||||||

| SS | 敏感電路 | |||||||

| SW | 鐘錶電路 | |||||||

C—符合國家標準

T—TTL電路

54S20—肖特基雙4輸入與非門

M—‐55~125℃

D—多層陶瓷雙列直插封裝

1、BGA

(ball grid array)

BGA

BGA 球形觸點陣列,表面貼裝型封裝之一。在印刷基板的背面按陣列方式製作出球形 凸點用 以代替引腳,在印刷基板的正面裝配LSI 晶片,然後用模壓樹脂或灌封方法進行密封。也稱為凸點陣列載體(PAC)。引腳可超過200,是多引腳LSI 用的一種封裝。封裝本體也可做得比QFP(四側引腳扁平封裝)小。例如,引腳中心距為1.5mm 的360引腳BGA僅為31mm 見方;而引腳中心距為0.5mm 的304 引腳QFP為40mm見方。而且BGA不用擔心QFP 那樣的引腳變形問題(見有圖所示)。

2、BQFP

(quad flat package with bumper)

帶緩衝墊的四側引腳扁平封裝。 QFP封裝之一,在封裝本體的四個角設定突起(緩衝墊)以防止在運送過程中引腳發生彎曲變形。美國半導體廠家主要在微處理器和ASIC等電路中採用此封裝。引腳中心距0.635mm,引腳數從84 到196 左右(見QFP)。

3、C-

(ceramic)

表示陶瓷封裝的記號。例如,CDIP 表示的是 陶瓷DIP。是在實際中經常使用的記號。

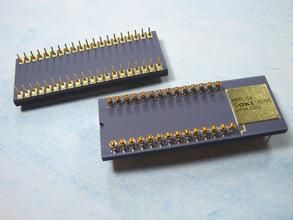

4、Cerdip

用玻璃密封的陶瓷雙列直插式封裝,用於ECL RAM,DSP(數位訊號處理器)等電路。帶有 玻璃視窗的Cerdip 用於紫外線擦除型EPROM以及內部帶有EPROM 的微機電路等。引腳中心距2.54mm,引腳數從8到42。在日本,此封裝表示為DIP-G(G即玻璃密封的意思)。

5、Cerquad

表面貼裝型封裝之一,即用下密封的陶瓷QFP,用於封裝DSP 等的邏輯LSI 電路。帶有視窗的Cerquad 用於封裝EPROM 電路。散熱性比塑膠QFP 好,在自然空冷條件下可容許1.5~2W 的功率。但封裝成本比塑膠QFP 高3~5 倍。引腳中心距有1.27mm、0.8mm、0.65mm、 0.5mm、 0.4mm 等多種規格。引腳數從32 到368。

帶引腳的陶瓷晶片載體,表面貼裝型封裝之一,引腳從封裝的四個側面引出,呈丁字形。帶有視窗的用於封裝紫外線擦除型EPROM 以及帶有EPROM 的微機電路等。此封裝也稱為 QFJ、QFJ-G(見QFJ)。

6、COB

(chip on board)

板上晶片封裝,是裸晶片貼裝技術之一,半導體晶片交接貼裝在印刷線路板上,晶片與基板的電氣連線用引線縫合方法實現,晶片與基板的電氣連線用引線縫合方法實現,並用樹脂覆蓋以確保可靠性。雖然COB是最簡單的裸晶片貼裝技術,但它的封裝密度遠不如TAB 和 倒片 焊技術。

7、DFP

(dual flat package)

雙側引腳扁平封裝。是SOP 的別稱(見SOP)。以前曾有此稱法,80年代後期已 基本上不用。

8、DIC

(dual in-line ceramic package)

陶瓷DIP(含玻璃密封)的別稱(見DIP).

9、DIL

(dual in-line)

DIP 的別稱(見DIP)。歐洲半導體廠家多用此名稱。

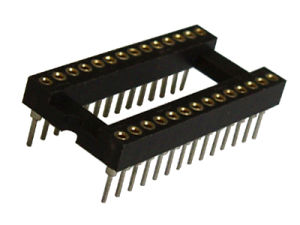

10、DIP

(dual in-line package)

雙列直插式封裝。插裝型封裝之一,引腳從封裝兩側引出,封裝材料有塑膠和陶瓷兩種 。 DIP 是最普及的插裝型封裝,套用範圍包括標準邏輯IC,存貯器LSI,微機電路等。 引腳中心距2.54mm,引腳數從6 到64。封裝寬度通常為15.2mm。有的把寬度為7.52mm 和10.16mm 的封裝分別稱為skinny DIP 和slim DIP(窄體型DIP)。但多數情況下並不加區分,只簡單地統稱為DIP。另外,用低熔點玻璃密封的陶瓷DIP也稱為cerdip(見cerdip)。

11、DSO

(dual small out-lint)

雙側引腳小外形封裝。SOP 的別稱(見SOP)。部分半導體廠家採用此名稱。

12、DICP

(dual tape carrier package)

雙側引腳帶載封裝。TCP( 帶載封裝)之一。引腳製作在絕緣帶上並從封裝兩側引出。由於利用的是TAB(自動帶載焊接)技術,封裝外形非常薄。常用於液晶顯示驅動LSI,但多數為 定製品。 另外,0.5mm 厚的存儲器LSI 簿形封裝正處於開發階段。在日本,按照EIAJ(日本電子機 械工 業)會標準規定,將DICP 命名為DTP。

13、DIP

(dual tape carrier package)

同上。日本電子機械工業會標準對DTCP 的命名(見DTCP)。

14、FP

(flat package)

扁平封裝。表面貼裝型封裝之一。QFP 或SOP(見QFP 和SOP)的別稱。部分半導體廠家采 用此名稱。

15、flip-chip

倒焊晶片。裸晶片封裝技術之一,在LSI 晶片的電極區製作好金屬凸點,然後把金屬凸點與印刷基板上的電極區進行壓焊連線。封裝的占有面積基本上與晶片尺寸相同。是所有 封裝技術中體積最小、最薄的一種。但如果基板的熱膨脹係數與LSI 晶片不同,就會在接合處產生反應,從而影響連線的可靠性。因此必須用樹脂來加固LSI 晶片,並使用熱膨脹係數基本相同的基板材料。

16、FQFP

(fine pitch quad flat package)

小引腳中心距QFP。通常指引腳中心距小於0.65mm 的QFP(見QFP)。部分導導體廠家採用此名稱。

17、CPAC

(globe top pad array carrier)

美國Motorola 公司對BGA 的別稱(見BGA)。

18、CQFP

(quad fiat package with guard ring)

帶保護環的四側引腳扁平封裝。塑膠QFP 之一,引腳用樹脂保護環 掩蔽,以防止彎曲變 形。在把LSI 組裝在印刷基板上之前,從保護環處切斷引腳並使其成為海鷗翼狀(L 形狀)。這種封裝 在美國Motorola 公司已批量生產。引腳中心距0.5mm,引腳數最多為208 左右。

19、H-

(with heat sink)

表示帶散熱器的標記。例如,HSOP 表示帶散熱器的SOP。

20、pin grid array

(surface mount type)

表面貼裝型PGA。通常PGA 為插裝型封裝,引腳長約3.4mm。表面貼裝型PGA 在封裝的 底面有陳列狀的引腳,其長度從1.5mm 到2.0mm。貼裝採用與印刷基板碰焊的方法,因而 也稱 為碰焊PGA。因為引腳中心距只有1.27mm,比插裝型PGA 小一半,所以封裝本體可製作得 不 怎么大,而引腳數比插裝型多(250~528),是大規模邏輯LSI 用的封裝。封裝的基材有 多層陶 瓷基板和玻璃環氧樹脂印刷基數。以多層陶瓷基材製作封裝已經實用化。

21、JLCC

(J-leaded chip carrier)

J 形引腳晶片載體。指帶視窗CLCC 和帶視窗的陶瓷QFJ的別稱(見CLCC 和QFJ)。部分半導體廠家採用的名稱。

22、LCC

LCC

LCC (Leadless chip carrier)

無引腳晶片載體。指陶瓷基板的四個側面只有電極接觸而無引腳的表面貼裝型封裝。是 高速和高頻IC 用封裝,也稱為陶瓷QFN 或QFN-C(見QFN)。

23、LGA

(land grid array)

觸點陳列封裝。即在底面製作有陣列狀態坦電極觸點的封裝。裝配時插入插座即可。現 已 實用的有227 觸點(1.27mm 中心距)和447 觸點(2.54mm 中心距)的陶瓷LGA,套用於高速 邏輯 LSI 電路。 LGA 與QFP 相比,能夠以比較小的封裝容納更多的輸入輸出引腳。另外,由於引線的阻 抗 小,對於高速LSI 是很適用的。但由於插座製作複雜,成本高,90年代基本上不怎么使用 。預計 今後對其需求會有所增加。

24、LOC

(lead on chip)

晶片上引線封裝。LSI 封裝技術之一,引線框架的前端處於晶片上方的一種結構,晶片的中心附近製作有凸焊點,用引線縫合進行電氣連線。與原來把引線框架布置在晶片側面 附近的 結構相比,在相同大小的封裝中容納的晶片達1mm 左右寬度。

25、LQFP

(low profile quad flat package)

薄型QFP。指封裝本體厚度為1.4mm 的QFP,是日本電子機械工業會根據制定的新QFP 外形規格所用的名稱。

26、L-QUAD

陶瓷QFP 之一。封裝基板用氮化鋁,基導熱率比氧化鋁高7~8 倍,具有較好的散熱性。 封裝的框架用氧化鋁,晶片用灌封法密封,從而抑制了成本。是為邏輯LSI 開發的一種 封裝,在自然空冷條件下可容許W3的功率。現已開發出了208 引腳(0.5mm 中心距)和160 引腳 (0.65mm 中心距)的LSI 邏輯用封裝,並於1993 年10 月開始投入批量生產。

27、MCM

(multi-chip module)

多晶片組件。將多塊半導體裸晶片組裝在一塊布線基板上的一種封裝。根據基板材料可分為MCM-L,MCM-C 和MCM-D 三大類。 MCM-L 是使用通常的玻璃環氧樹脂多層印刷基板的組件。布線密度不怎么高,成本較低 。 MCM-C 是用厚膜技術形成多層布線,以陶瓷(氧化鋁或玻璃陶瓷)作為基板的組件,與使 用多層陶瓷基板的厚膜混合IC 類似。兩者無明顯差別。布線密度高於MCM-L。

MCM-D 是用薄膜技術形成多層布線,以陶瓷(氧化鋁或氮化鋁)或Si、Al 作為基板的組件。布線密謀在三種組件中是最高的,但成本也高。

28、MFP

(mini flat package)

小形扁平封裝。塑膠SOP 或SSOP 的別稱(見SOP 和SSOP)。部分半導體廠家採用的名稱。

29、MQFP

(metric quad flat package)

按照JEDEC(美國聯合電子設備委員會)標準對QFP 進行的一種分類。指引腳中心距為 0.65mm、本體厚度為3.8mm~2.0mm 的標準QFP(見QFP)。

30、MQUAD

(metal quad)

美國Olin 公司開發的一種QFP 封裝。基板與封蓋均採用 鋁材,用粘合劑密封。在自然空冷條件下可容許2.5W~2.8W 的功率。日本新光電氣工業公司於1993 年獲得特許開始生產 。

31、MSP

(mini square package)

QFI 的別稱(見QFI),在開發初期多稱為MSP。QFI 是日本電子機械工業會規定的名稱。

34、OPMAC(over molded pad array carrier)

模壓樹脂密封凸點陳列載體。美國Motorola 公司對模壓樹脂密封BGA 採用的名稱(見 BGA)。

32、P-

(plastic)

表示塑膠封裝的記號。如PDIP 表示塑膠DIP。

33、PAC

(pad array carrier)

凸點陳列載體,BGA 的別稱(見BGA)。

34、PCLP

(printed circuit board leadless package)

印刷電路板無引線封裝。日本富士通公司對塑膠QFN(塑膠LCC)採用的名稱(見QFN)。引

腳中心距有0.55mm 和0.4mm 兩種規格。

35、PFPF

(plastic flat package)

塑膠扁平封裝。塑膠QFP 的別稱(見QFP)。部分LSI 廠家採用的名稱。

36、PGA

(pin grid array)

陳列引腳封裝。插裝型封裝之一,其底面的垂直引腳呈陳列狀排列。封裝基材基本上都採用多層陶瓷基板。在未專門表示出材料名稱的情況下,多數為陶瓷PGA,用於高速大規模 邏輯 LSI 電路。成本較高。引腳中心距通常為2.54mm,引腳數從64 到447 左右。 了為降低成本,封裝基材可用玻璃環氧樹脂印刷基板代替。也有64~256 引腳的塑膠PG A。 另外,還有一種引腳中心距為1.27mm 的短引腳表面貼裝型PGA(碰焊PGA)。(見表面貼裝 型PGA)。

37、piggy back

馱載封裝。指配有插座的陶瓷封裝,形關與DIP、QFP、QFN 相似。在開發帶有微機的設 備時用於評價程式確認操作。例如,將EPROM 插入插座進行調試。這種封裝基本上都是 定製 品,市場上不怎么流通。

38、

PLCC

PLCC (plastic leaded chip carrier)

帶引線的塑膠晶片載體。表面貼裝型封裝之一。引腳從封裝的四個側面引出,呈丁字形 ,是塑膠製品。美國德克薩斯儀器公司首先在64k 位DRAM 和256kDRAM 中採用,90年代已經 普 及用於邏輯LSI、DLD(或程邏輯器件電路。引腳中心距1.27mm,引腳數從18 到84。 J 形引腳不易變形,比QFP 容易操作,但焊接後的外觀檢查較為困難。 PLCC 與LCC(也稱QFN)相似。以前,兩者的區別僅在於前者用塑膠,後者用陶瓷。但現 在已經出現用陶瓷製作的J 形引腳封裝和用塑膠製作的無引腳封裝(標記為 塑膠LCC、PC LP、P -LCC 等),已經無法分辨。為此,日本電子機械工業會於1988 年決定,把從四側引出 J 形引 腳的封裝稱為QFJ,把在四側帶有電極凸點的封裝稱為QFN(見QFJ 和QFN)。

39、P-LCC

(plastic teadless chip carrier)(plastic leaded chip currier)

有時候是塑膠QFJ 的別稱,有時候是QFN(塑膠LCC)的別稱(見QFJ 和QFN)。部分LSI 廠家用PLCC 表示帶引線封裝,用P-LCC 表示無引線封裝,以示區別。

40、QFH

(quad flat high package)

四側引腳厚體扁平封裝。塑膠QFP 的一種,為了防止封裝本體斷裂,QFP 本體製作得 較厚(見QFP)。部分半導體廠家採用的名稱。

41、QFI

(quad flat I-leaded packgac)

四側I 形引腳扁平封裝。表面貼裝型封裝之一。引腳從封裝四個側面引出,向下呈I 字 。 也稱為MSP(見MSP)。貼裝與印刷基板進行碰焊連線。由於引腳無突出部分,貼裝占有面 積小 於QFP。 日立製作所為視頻模擬IC 開發並使用了這種封裝。此外,日本的Motorola 公司的PLL IC 也採用了此種封裝。引腳中心距1.27mm,引腳數從18 於68。

42、QFJ

(quad flat J-leaded package)

四側J 形引腳扁平封裝。表面貼裝封裝之一。引腳從封裝四個側面引出,向下呈J字形。是日本電子機械工業會規定的名稱。引腳中心距1.27mm。

材料有塑膠和陶瓷兩種。塑膠QFJ 多數情況稱為PLCC(見PLCC),用於微機、門陳列、 DRAM、ASSP、OTP 等電路。引腳數從18 至84。

陶瓷QFJ 也稱為CLCC、JLCC(見CLCC)。帶視窗的封裝用於紫外線擦除型EPROM 以及帶有EPROM 的微機晶片電路。引腳數從32 至84。

43、QFN

(quad flat non-leaded package)

四側無引腳扁平封裝。表面貼裝型封裝之一。90年代後期多稱為LCC。QFN 是日本電子機械工業會規定的名稱。封裝四側配置有電極觸點,由於無引腳,貼裝占有面積比QFP 小,高度 比QFP 低。但是,當印刷基板與封裝之間產生應力時,在電極接觸處就不能得到緩解。因此電 極觸點 難於作到QFP 的引腳那樣多,一般從14 到100 左右。 材料有陶瓷和塑膠兩種。當有LCC 標記時基本上都是陶瓷QFN。電極觸點中心距1.27mm。

塑膠QFN 是以 玻璃環氧樹脂印刷基板基材的一種 低成本封裝。電極觸點中心距除1.27mm 外, 還有0.65mm 和0.5mm 兩種。這種封裝也稱為塑膠LCC、PCLC、P-LCC 等。

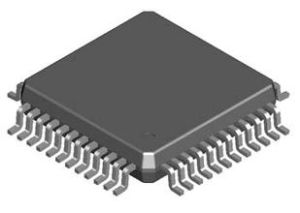

44、QFP

(quad flat package)

四側引腳扁平封裝。表面貼裝型封裝之一,引腳從四個側面引出呈海鷗翼(L)型。基材有 陶 瓷、金屬和塑膠三種。從數量上看,塑膠封裝占絕大部分。當沒有特別表示出材料時, 多數情 況為塑膠QFP。塑膠QFP 是最普及的多引腳LSI 封裝。不僅用於微處理器,門陳列等數字 邏輯LSI 電路,而且也用於VTR 信號處理、音響信號處理等模擬LSI 電路。引腳中心距 有1.0mm、0.8mm、 0.65mm、0.5mm、0.4mm、0.3mm 等多種規格。0.65mm 中心距規格中最多引腳數為304。

日本將引腳中心距小於0.65mm 的QFP 稱為QFP(FP)。但2000年後日本電子機械工業會對QFP 的外形規格進行了重新評價。在引腳中心距上不加區別,而是根據封裝本體厚度分為 QFP(2.0mm~3.6mm 厚)、LQFP(1.4mm 厚)和TQFP(1.0mm 厚)三種。

另外,有的LSI 廠家把引腳中心距為0.5mm 的QFP 專門稱為收縮型QFP 或SQFP、VQFP。 但有的廠家把引腳中心距為0.65mm 及0.4mm 的QFP 也稱為SQFP,至使名稱稍有一些混亂 。 QFP 的缺點是,當引腳中心距小於0.65mm 時,引腳容易彎曲。為了防止引腳變形,現已 出現了幾種改進的QFP 品種。如封裝的四個角帶有樹指緩衝墊的BQFP(見BQFP);帶樹脂 保護 環覆蓋引腳前端的GQFP(見GQFP);在封裝本體裡設定測試凸點、放在防止引腳變形的專 用夾 具里就可進行測試的TPQFP(見TPQFP)。 在邏輯LSI 方面,不少開發品和高可靠品都封裝在多層陶瓷QFP 里。引腳中心距最小為 0.4mm、引腳數最多為348 的產品也已問世。此外,也有用玻璃密封的陶瓷QFP(見Gerqa d)。

45、QFP

(FP)(QFP fine pitch)

小中心距QFP。日本電子機械工業會標準所規定的名稱。指引腳中心距為0.55mm、0.4mm 、 0.3mm 等小於0.65mm 的QFP(見QFP)。

46、QIC

(quad in-line ceramic package)

陶瓷QFP 的別稱。部分半導體廠家採用的名稱(見QFP、Cerquad)。

47、QIP

(quad in-line plastic package)

塑膠QFP 的別稱。部分半導體廠家採用的名稱(見QFP)。

48、QTCP

(quad tape carrier package)

四側引腳帶載封裝。TCP 封裝之一,在絕緣帶上形成引腳並從封裝四個側面引出。是利 用 TAB 技術的薄型封裝(見TAB、TCP)。

49、

QTP

QTP (quad tape carrier package)

四側引腳帶載封裝。日本電子機械工業會於1993 年4 月對QTCP 所制定的外形規格所用 的 名稱(見TCP)。

50、QUIL

(quad in-line)

QUIP 的別稱(見QUIP)。

51、QUIP

(quad in-line package)

四列引腳直插式封裝。引腳從封裝兩個側面引出,每隔一根交錯向下彎曲成四列。引腳 中 心距1.27mm,當插入印刷基板時,插入中心距就變成2.5mm。因此可用於標準印刷線路板。是 比標準DIP 更小的一種封裝。日本電氣公司在台式計算機和家電產品等的微機晶片中采 用了些 種封裝。材料有陶瓷和塑膠兩種。引腳數64。

52、SDIP

(shrink dual in-line package)

收縮型DIP。插裝型封裝之一,形狀與DIP 相同,但引腳中心距(1.778mm)小於DIP(2.54 mm),

因而得此稱呼。引腳數從14 到90。也有稱為SH-DIP 的。材料有陶瓷和塑膠兩種。

53、SH-DIP

(shrink dual in-line package)

同SDIP。部分半導體廠家採用的名稱。

54、SIL

(single in-line)

SIP 的別稱(見SIP)。歐洲半導體廠家多採用SIL 這個名稱。

55、SIMM

(single in-line memory module)

單列存貯器組件。只在印刷基板的一個側面附近配有電極的存貯器組件。通常指插入插 座 的組件。標準SIMM 有中心距為2.54mm 的30 電極和中心距為1.27mm 的72 電極兩種規格 。 在印刷基板的單面或雙面裝有用SOJ 封裝的1 兆位及4 兆位DRAM 的SIMM 已經在個人 計算機、工作站等設備中獲得廣泛套用。至少有30~40%的DRAM 都裝配在SIMM 里。

56、SIP

(single in-line package)

單列直插式封裝。引腳從封裝一個側面引出,排列成一條直線。當裝配到印刷基板上時 封 裝呈側立狀。引腳中心距通常為2.54mm,引腳數從2 至23,多數為定製產品。封裝的形 狀各 異。也有的把形狀與ZIP 相同的封裝稱為SIP。

57、SK-DIP

(skinny dual in-line package)

DIP 的一種。指寬度為7.62mm、引腳中心距為2.54mm 的窄體DIP。通常統稱為DIP(見 DIP)。

58、SL-DIP

(slim dual in-line package)

DIP 的一種。指寬度為10.16mm,引腳中心距為2.54mm 的窄體DIP。通常統稱為DIP。

59、SMD

(surface mount devices)

表面貼裝器件。偶而,有的半導體廠家把SOP 歸為SMD(見SOP)。

SOP 的別稱。世界上很多半導體廠家都採用此別稱。(見SOP)。

60、SOI

(small out-line I-leaded package)

I 形引腳小外型封裝。表面貼裝型封裝之一。引腳從封裝雙側引出向下呈I 字形,中心 距 1.27mm。貼裝占有面積小於SOP。日立公司在模擬IC(電機驅動用IC)中採用了此封裝。引 腳數 26。

61、SOIC

(small out-line integrated circuit)

SOP 的別稱(見SOP)。國外有許多半導體廠家採用此名稱。

62、SOJ

(Small Out-Line J-Leaded Package)

J 形引腳小外型封裝。表面貼裝型封裝之一。引腳從封裝兩側引出向下呈J 字形,故此 得名。 通常為塑膠製品,多數用於DRAM 和SRAM 等存儲器LSI 電路,但絕大部分是DRAM。用SO J 封裝的DRAM 器件很多都裝配在SIMM 上。引腳中心距1.27mm,引腳數從20 至40(見SIMM )。

63、SQL

(Small Out-Line L-leaded package)

按照JEDEC(美國聯合電子設備工程委員會)標準對SOP 所採用的名稱(見SOP)。

64、SONF

(Small Out-Line Non-Fin)

無散熱片的SOP。與通常的SOP 相同。為了在功率IC 封裝中表示無散熱片的區別,有意 增添了NF(non-fin)標記。部分半導體廠家採用的名稱(見SOP)。

65、SOP

(small Out-Line package)

小外形封裝。表面貼裝型封裝之一,引腳從封裝兩側引出呈海鷗翼狀(L 字形)。材料有 塑膠 和陶瓷兩種。另外也叫SOL 和DFP。

SOP 除了用於存儲器LSI 外,也廣泛用於規模不太大的ASSP 等電路。在輸入輸出端子不 超過10~40 的領域,SOP 是普及最廣的表面貼裝封裝。引腳中心距1.27mm,引腳數從8 ~44。

另外,引腳中心距小於1.27mm 的SOP 也稱為SSOP;裝配高度不到1.27mm 的SOP 也稱為 TSOP(見SSOP、TSOP)。還有一種帶有散熱片的SOP。

66、SOW

(Small Outline Package(Wide-Jype))

寬體SOP。部分半導體廠家採用的名稱。

製造

從1930年代開始,元素周期表中的化學元素中的半導體被研究者如貝爾實驗室的William Shockley認為是固態真空管的最可能的原料。從氧化銅到鍺,再到矽,原料在1940到1950年代被系統的研究。今天,儘管元素周期表的一些III-V價化合物如砷化鎵套用於特殊用途如:發光二極體,雷射,太陽能電池和最高速積體電路,單晶矽成為積體電路主流的基層。創造無缺陷晶體的方法用去了數十年的時間。

半導體IC製程,包括以下步驟,並重複使用:

黃光(微影)

蝕刻

薄膜

擴散

CMP

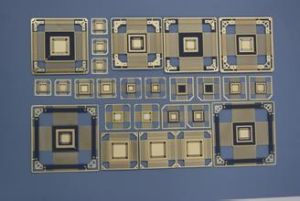

使用單晶矽晶圓(或III-V族,如砷化鎵)用作基層。然後使用 微影、擴散、CMP等技術製成MOSFET或BJT等組件,然後利用微影、薄膜、和CMP技術製成導線,如此便完成晶片製作。因產品性能需求及成本考量,導線可分為鋁製程和銅製程。 IC 由很多重疊的層組成,每層由圖像技術定義,通常用不同的顏色表示。一些層標明在哪裡不同的摻雜劑擴散進基層(成為擴散層),一些定義哪裡額外的離子灌輸(灌輸層),一些定義導體(多晶矽或金屬層),一些定義傳導層之間的連線(過孔或接觸層)。所有的組件由這些層的特定組合構成。

在一個自排列(CMOS)過程中,所有門層(多晶矽或金屬)穿過擴散層的地方形成電晶體。

電阻結構,電阻結構的長寬比,結合表面電阻係數,決定電阻。

電容結構,由於尺寸限制,在IC上只能產生很小的電容。

更為少見的電感結構,可以製作晶片載電感或由迴旋器模擬。

因為CMOS設備只引導電流在邏輯門之間轉換,CMOS設備比雙級組件消耗的 電流少很多。

隨機存取存儲器(random access memory)是最常見類型的積體電路,所以密度最高的設備是存儲器,但即使是微處理器上也有存儲器。儘管結構非常複雜-幾十年來晶片寬度一直減少-但積體電路的層依然比寬度薄很多。組件層的製作非常像照相過程。雖然可見光譜中的光波不能用來曝光組件層,因為他們太大了。高頻光子(通常是紫外線)被用來創造每層的圖案。因為每個特徵都非常小,對於一個正在調試製造過程的過程工程師來說,電子顯微鏡是必要工具。

在使用自動測試設備(ATE)包裝前,每個設備都要進行測試。測試過程稱為晶圓測試或 晶圓探通。晶圓被切割成矩形塊,每個被稱為“die”。每個好的die 被焊在“pads”上的鋁線或金線,連線到封裝內,pads通常在die的邊上。封裝之後,設備在晶圓探通中使用的相同或相似的ATE上進行終檢。測試成本可以達到低成本產品的製造成本的25%,但是對於低產出,大型和/或高成本的設備,可以忽略不計。

在2005年,一個製造廠(通常稱為半導體工廠,常簡稱fab,指fabrication facility)建設費用要超過10億美金,因為大部分操作是自動化的。

發展趨勢

2001年到2010年這10年間,我國積體電路產量的年均增長率超過25%,積體電路銷售額的年均增長率則達到23%。2010年國內積體電路產量達到640億塊,銷

售額超過1430億元,分別是2001年的10倍和8倍。中國積體電路產業規模已經由2001年不足世界積體電路產業總規模的2%提高到2010年的近9%。中國成為過去10年世界積體電路產業發展最快的地區之一。國內積體電路市場規模也由2001年的1140億元擴大到2010年的7350億元,擴大了6.5倍。國內積體電路產業規模與市場規模之比始終未超過20%。如扣除積體電路產業中接受境外委託代工的銷售額,則中國積體電路市場的實際國內自給率還不足10%,國內市場所需的積體電路產品主要依靠進口。近幾年國內積體電路進口規模迅速擴大,2010年已經達到創紀錄的1570億美元,積體電路已連續兩年超過原油成為國內最大宗的進口商品。與巨大且快速增長的國內市場相比,中國積體電路產業雖發展迅速但仍難以滿足內需要求。

當前以移動網際網路、三網融合、物聯網、雲計算、智慧型電網、新能源汽車為代表的戰略性新興產業快速發展,將成為繼計算機、網路通信、消費電子之後,推動積體電路產業發展的新動力。工信部預計,國內積體電路市場規模到2015年將達到12000億元。

我國積體電路產業發展的生態環境亟待最佳化,設計、製造、封裝測試以及專用設備、儀器、材料等產業鏈上下游協同性不足,晶片、軟體、整機、系統、套用等各環節互動不緊密。“十二五”期間,中國將積極探索積體電路產業鏈上下游虛擬一體化模式,充分發揮市場機製作用,強化產業鏈上下游的合作與協同,共建價值鏈。培育和完善生態環境,加強積體電路產品設計與軟體、整機、系統及服務的有機連線,實現各環節企業的群體躍升,增強電子信息大產業鏈的整體競爭優勢。

其他信息

電晶體

電晶體 IC 對於離散電晶體有兩個主要優勢:成本和性能。成本低是由於晶片把所有的組件通過照相 平版技術,作為一個單位印刷,而不是在一個時間只製作一個電晶體。性能高是由於組件快速開關,消耗更低能量,因為組件很小且彼此靠近。2006年,晶片面積從幾平方毫米到350 mm2,每mm2可以達到一百萬個電晶體。

第一個積體電路雛形是由傑克·基爾比於1958年完成的,其中包括一個雙極性電晶體,三個電阻和一個電容器。

根據一個晶片上集成的微電子器件的數量,積體電路可以分為以下幾類:

1.小規模積體電路

SSI 英文全名為 Small Scale Integration, 邏輯門10個以下 或 電晶體 100個以下。

2.中規模積體電路

MSI 英文全名為 Medium Scale Integration, 邏輯門11~100個 或 電晶體 101~1k個。

3.大規模積體電路

LSI 英文全名為 Large Scale Integration, 邏輯門101~1k個 或 電晶體 1,001~10k個。

4.超大規模積體電路

VLSI 英文全名為 Very large scale integration, 邏輯門1,001~10k個 或 電晶體 10,001~100k個。

5.甚大規模積體電路

ULSI 英文全名為 Ultra Large Scale Integration, 邏輯門10,001~1M個 或 電晶體 100,001~10M個。

GLSI 英文全名為 Giga Scale Integration, 邏輯門1,000,001個以上 或 電晶體10,000,001個以上。

而根據處理信號的不同,可以分為模擬積體電路、數字積體電路、和兼具模擬與數字的混合信號積體電路。

發展

最先進的積體電路是微處理器或多核處理器的"核心(cores)",可以控制電腦到手機到數字微波爐的一切。存儲器和ASIC是其他積體電路家族的例子,對於現代信息社會非常重要。雖然設計開發一個複雜積體電路的成本非常高,但是當分散到通常以百萬計的產品上,每個IC的成本最小化。IC的性能很高,因為小尺寸帶來短路徑,使得低功率邏輯電路可以在快速開關速度套用。

IC 持續向更小的外型尺寸發展,使得每個晶片可以封裝更多的電路。這樣增加了每單位面積容量,可以降低成本和增加功能-見摩爾定律,積體電路中的電晶體數量,每兩年增加一倍。總之,隨著外形尺寸縮小,幾乎所有的指標改善了-單位成本和開關功率消耗下降,速度提高。但是,集成納米級別設備的IC不是沒有問題,主要是泄漏電流(leakage current)。因此,對於最終用戶的速度和功率消耗增加非常明顯,製造商面臨使用更好幾何學的尖銳挑戰。這個過程和在未來幾年所期望的進步,在半導體國際技術路線圖(ITRS)中有很好的描述。

越來越多的電路以集成晶片的方式出現在設計師手裡,使電子電路的開發趨向於小型化、高速化。越來越多的套用已經由複雜的模擬電路轉化為簡單的數字邏輯積體電路。

IC的普及

僅僅在其開發後半個世紀,積體電路變得無處不在,電腦,手機和其他數字電器成為現代社會結構不可缺少的一部分。這是因為,現代計算,交流,製造和交通系統,包括網際網路,全都依賴於積體電路的存在。甚至很多學者認為有積體電路帶來的數字革命是人類歷史中最重要的事件。

IC的分類

積體電路的分類方法很多,依照電路屬模擬或數字,可以分為:模擬積體電路、數字積體電路和混合信號積體電路(模擬和數字在一個晶片上)。

數字積體電路可以包含任何東西,在幾平方毫米上有從幾千到百萬的邏輯門,觸發器,多任務器和其他電路。這些電路的小尺寸使得與板級集成相比,有更高速度,更低功耗並降低了製造成本。這些數字IC, 以微處理器,數位訊號處理器(DSP)和單片機為代表,工作中使用二進制,處理1和0信號。

模擬積體電路有,例如感測器,電源控制電路和運放,處理模擬信號。完成放大,濾波,解調,混頻的功能等。通過使用專家所設計、具有良好特性的模擬積體電路,減輕了電路設計師的重擔,不需凡事再由基礎的一個個電晶體處設計起。

IC可以把模擬和數字電路集成在一個單晶片上,以做出如模擬數字轉換器(A/D converter)和數字模擬轉換器(D/A converter)等器件。這種電路提供更小的尺寸和更低的成本,但是對於信號衝突必須小心。

現狀

積體電路

積體電路 積體電路作為信息安全的基礎,是各種自主可控設備的重要支撐,國產化空間巨大。公司方面,通富微電擬併購AMD的封測業務,獲得了積體電路國家基金支持;太極實業旗下的海太半導體在DRAM封測領域競爭力較強。

隨著基礎設施的逐步完備,從PC到智慧型手機、平板電腦,再到冰、洗、空等大家電的聯網化、智慧型化對晶片產業都有顯著推動作用。穿戴式設備、汽車、家居等也已經開始了聯網化、智慧型化的進程。未來連線一切的“ 物聯網”已經隱約可見。

全球積體電路產業的高景氣度,為國內產業發展提供了良好的環境。不僅如此,在 景氣周期的基礎上,國內產業還疊加了技術進步周期和政策扶持周期。天時地利人和齊備,使得積體電路產業在國內也表現出更多的成長性特徵。自2013年開始,全球晶片產業銷售額開啟了新一輪增長周期。

我們認為,本次景氣周期將是溫和的,產值的增速會在5%~10%之間,但會持續3~5年時間,這將顯著區別於PC時代景氣度隨換機周期和技術進步影響而 大幅波動的狀況。