基本信息

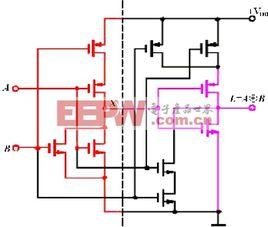

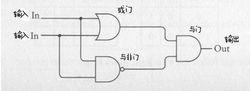

雖然異或不是開關代數的基本運算之一,但是在實際運用中相當普遍地使用分立的異或門。大多數開關技術不能直接實現異或功能,而是使用多個門設計。

異或門

異或門邏輯表達式:(⊕為“異或”運算符)

真值表:

| A | B | 輸出Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

實現

異或門邏輯電路(門級) 異或門邏輯電路(門級) |

異或門 能實現模為2的加法,因此,異或門可以實現計算機中的二進制加法。半加器就是由異或門和與門組成的。

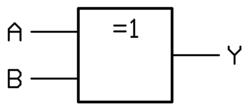

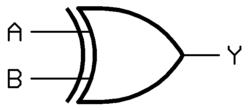

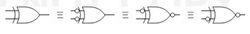

符號

異或門的常用邏輯符號如下圖所示。對異或門的任何2個信號(輸入或輸出)同時取反,而不改變結果的邏輯功能。在“圈到圈”的設計中,我們選用最能表達要實現的邏輯功能的符號。

IEC 60617-12 IEC 60617-12 |  ANSI/IEEE Std 91-1984 ANSI/IEEE Std 91-1984 |  異或門的等效符號 異或門的等效符號 |