集成注入邏輯電路

正文

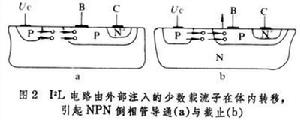

在NPN電晶體的基極接有PNP電晶體作為恆流源,採用公共發射區,集成多個NPN電晶體倒相器的基本門電路,簡稱I2L電路。將這類基本門電路前後串接起來,經過適當組合,即可實現各種邏輯功能。在前後串接組合時,本級恆流源電流既可作為前級的負載電流,又可作為本級基極注入電流,這取決於前級門的狀態是通導還是截止。I2L電路是70年代初發展起來的一種高集成密度、雙極型邏輯電路。它是在常規雙極型積體電路工藝的基礎上經過改進而成。I2L電路無需隔離,結構緊湊,不用電阻,可以獲得很高的集成度和集成密度,並在低功耗下有較高的速度。

I2L電路採用PNP橫向電晶體作為恆流源。橫向電晶體是指PNP或NPN電晶體的發射區、基區、集電區是沿晶片的平面方向分布,即從發射極到集電極的電流是在晶片內橫向流動。矽雙極型積體電路主要用 NPN電晶體構成。在以 NPN電晶體為主體的積體電路中,如需要兼用PNP電晶體時,其方法之一是製作橫向PNP電晶體。橫向PNP電晶體製作簡單,能與NPN電晶體工藝兼容,不增加工序。在擴散NPN電晶體基區的同時,即可製作橫向PNP電晶體的發射區和集電區(發射區作為注入條也可再擴散,加深摻雜濃度)。橫向 PNP電晶體的缺點是截止頻率較低,電流放大係數在2~5之間,少數可達10左右。

I2L電路的倒相管採用公共發射區的縱向NPN電晶體。它與通常的縱向NPN電晶體不同,其集電區在上方,公共發射區在下方。

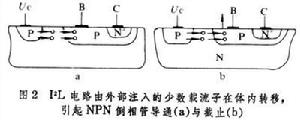

恆流源電晶體的發射極是一個P型注入條,橫向電晶體的基區和集電區,分別是縱向電晶體 NPN的發射區和基區。當P型注入條加上正電壓後(I2L電路的電源),注入條向 N型基區注入空穴,空穴渡越該基區後被集電區收集。被收集在 PNP電晶體集電區的空穴有兩個可能的去向:①作為NPN電晶體的基極注入電流(如果前級NPN電晶體處於截止狀態),導致NPN電晶體的導通;②作為前級NPN電晶體的集電極電流,如果前級NPN電晶體處於導通狀態,則該空穴電流流向前級 NPN電晶體。因其飽和壓降較小,本級NPN電晶體的發射結電壓也就很小,即本級NPN電晶體處於截止狀態(圖2)。因此,I2L電路的工作過程,實質上就是由外部注入條注入的少數載流子在集成器件體內轉移,引起基本門導通或截止。

集成注入邏輯電路

集成注入邏輯電路 集成注入邏輯電路

集成注入邏輯電路參考書目

復旦大學微電子教研組編:《積體電路設計原理》,人民教育出版社,北京,1978。