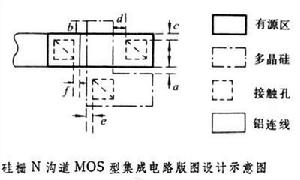

積體電路製作中,各類集成元件、器件及其間的隔離與互連等是在一套掩模版的控制下形成的。一套掩模版通常包括 4~10塊分版。每一塊分版是一組專門設計的圖形的集合,整套版中的各分版相互都要能精密地配合和對準。整套掩模版圖形(簡稱版圖)的設計,是把電路的元件、器件和互連線圖形化,用它來控制製備工藝,使積體電路獲得預期的性能、功能和效果。例如,增強型負載矽柵N溝道MOS型積體電路需要4塊分版,分別用以確定有源區、多晶矽、接觸孔和鋁連線。4組圖形的規則是:

有源區條寬與間距 6μm/6μm

多晶矽條寬與間距 8μm/6μm

接觸孔尺寸 6μm×6μm

鋁連線條寬與間距 6μm/6μm

多晶矽-有源區套刻量(ɑ) 2μm

多晶矽出頭長度(b)4μm

接觸孔-有源區套刻量(c) 2μm

接觸孔-有源區上多晶矽套刻量(d) 4μm

接觸孔-隔離區上多晶矽套刻量(e) 2μm

鋁連線-接觸孔套刻量(f) 2μm

積體電路版圖設計規則

積體電路版圖設計規則不同類型的積體電路所需要的分版數不同,具體的版圖設計規則也有差異。但制定版圖設計規則的基本原則則是一致的:①需要考慮工藝設備狀況(如光刻機的解析度和對準精度)和工藝技術水平(如工藝加工中,圖形尺寸側向變化量和控制);②避免寄生效應對積體電路的功能與電學性能的有害影響。

通常稱允許的最小圖形尺寸的平均值為特徵尺寸。它是對積體電路集成密度的度量,是積體電路工藝技術水平的一種標誌。