二極體-電晶體邏輯電路

正文

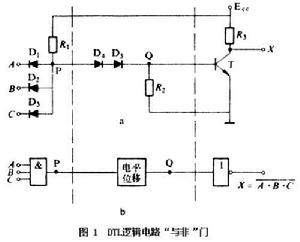

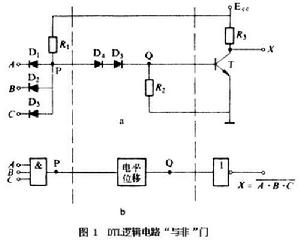

輸入端用二極體實現“與”邏輯,輸出端用電晶體實現“非”邏輯,採用二極體電平位移的單元門電路,簡稱DTL電路。其基本電路如圖1。在圖1a中的二極體D1、D2和D3完成“與”邏輯,二極體D4和D5提供補償電壓,電晶體T完成“非”邏輯,並提供增益。二極體D1、D2和D3的數目和“與”門輸入端A、B、C的數目相同,增加二極體可擴展輸入端數。 二極體-電晶體邏輯電路

二極體-電晶體邏輯電路 二極體-電晶體邏輯電路

二極體-電晶體邏輯電路參考書目

復旦大學微電子教研組編:《積體電路設計原理》,人民教育出版社,北京,1978。

沈鐸編:《半導體數字積體電路》,國防工業出版社,北京,1980。