多值邏輯與連續邏輯

正文

多值邏輯是正在發展中的現代科學領域之一。多值邏輯與古典邏輯中真值只能取“真”、“假”兩值不同,它可以取三個,四個,……,直至無限個。因而從哲學、邏輯學的角度,存在如何解釋各個真值的意義,以及多值邏輯和古典的二值邏輯的關係等問題。對於邏輯網路,顯然需要發展相當於布爾代數和開關理論的多值邏輯代數和多值邏輯網路的綜合、分析方法。發展多值硬體也是多值邏輯的主要課題之一。因而,所謂多值邏輯除了邏輯學的內容以外,還常指多值邏輯運算、多值電路及其套用等內容。1920年,波蘭學者J.盧卡西維奇在研究亞里士多德的未來偶然性問題時,首先提出了三值邏輯。1921年,美國學者E.L.波斯特假定命題的真值數目大於2,建立起任意有限多個值的邏輯系統。後來,人們在建立完備的多值邏輯演算系統、研究演算的性質和探索多穩態電路元件、多值電路方面進行了許多工作。

多值邏輯的運算手段稱多值代數。1921年,波斯特首先提出的多值代數完備集包括兩種運算

=0 其他情況

現代人們比較集中於低 R值特別是三值、四值邏輯的研究。對三值邏輯提出的J運算和T運算,受到廣泛的注意。J運算的定義為Jκ(x)=R-1 κ=x κ=0,1,2

=0

T(x1,x2,x3,κ)=x1 κ=0

=x2 κ=1

=x3 κ=2

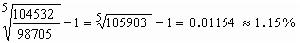

在多值網路的邏輯設計方面,類似二值情況,可對多值網路用上述基本運算進行分析、綜合。這方面的主要工作集中在R=3,4等低值情況,在分析和綜合多值網路時也採用二值情況下常用的真值表、卡諾圖等技術。但是,這要比二值時困難得多,主要是由於n個變數的R值函式,其真值表有Rn行,可構成R(R)n個不同函式。此數隨R的增加而迅速增加,如二變數二值函式計有2(2)2=16個,而二變數的三值函式則有3(3)2=19683個,分析就要困難得多。

多值邏輯工作中最大的困難是缺少合適的硬體來構成系統。早年曾希望研製出多穩態的固態器件替代二態的電晶體,但未見成效。現代按多值代數概念似乎只要有“max”、“min”配合一些單變數運算的門,原則上就有了足夠的多值基本門。用電晶體-電晶體邏輯電路、集成注入邏輯電路I2L、 互補金屬-氧化物-半導體積體電路、電荷耦合器件等各種電路形式構成的這類基本門都已有報導。同時,還可用二值電路多值編碼方案實現多值邏輯。但是,用這樣的方法進行系統設計,有的綜合範式複雜,有的所用門數超過相應的二值系統,不能體現多值邏輯的特點。1979年,E.J.麥克拉斯基從I2L實際電路出發,提出按電路連線情況選取接點的多值邏輯設計法。人們已在一些超大規模積體電路系列中成功地使用多值邏輯概念製成四值唯讀存儲器。其基本設計思想是:在存儲元件陣列中使用四種溝道尺寸的 MOS電晶體,分別表示四種狀態。陣列元件被選中時,自動與三個並聯的比較器接通,進行比較,輸出的三個比較結果,表示選中的是何種尺碼的MOS管,解碼後以二值編碼讀出。

多值邏輯電路與二值邏輯相比,優點是在同樣數目的出腿和連線情況下傳送的信息量增加;完成二值同樣的邏輯所需的門數可減少。存在的問題是多值信號傳輸中產生衰減,整形有困難;多值信號的閾值數目增加會減小噪聲影響,信號的容差要求比二值嚴;由於信號擺幅增加,速度比二值慢。在性能和經濟效益上,多值邏輯還不能全面超過二值系統,較多地用於指導和研製一些數字部件,進行邏輯系統調試、計算機的容差檢出等。

在多值邏輯和連續邏輯電路方面,1978年中國創新的多元邏輯電路(DYL)包含了連續邏輯max和min門,或稱為線性“與或”門。

參考書目

王憲鈞:《數理邏輯引論》,北京大學出版社,北京,1982。