簡介

乘法器(multiplier)可以通過使用一系列計算機算數技術來實現。大多數的技術涉及了對部分積(partial product)的計算(其過程和我們使用豎式手工計算多位十進制數乘法十分類似),然後將這些部分積相加起來。不過在這裡根據二進制的情況進行了修改。

雙平衡式四象限乘法器

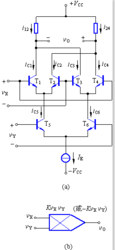

雙平衡式四象限乘法器理想乘法器的輸出特性方程可由下式表示:

UO(t)=KUX(t)UY(t)

式中 K--乘法器的相乘增益(乘法係數),其量綱為V-1。在模擬運算運算中常取K=1/10V-1。

作用

乘法器不僅作為乘法、除法、乘方和開方等模擬運算的主要基本單元,而且還廣泛用於電子通信系統作為調製、解調、混頻、鑒相和自動增益控制;另外還可用於濾波、波形形成和頻率控制等場合,因此是一種用途廣泛的功能電路。

一個理想的通用乘法器,不應當對任何一個輸入信號的極性加以限制,也就是說,應當具有能完成四個象限的運算功能的電路。

類型

模擬乘法器

乘法器

乘法器模擬乘法器是對兩個模擬信號(電壓或電流)實現相乘功能的的有源非線性器件。主要功能是實現兩個互不相關信號相乘,即輸出信號與兩輸入信號相乘積成正比。它有兩個輸入連線埠,即X和Y輸入連線埠。

乘法器兩個輸入信號的極性不同,其輸出信號的極性也不同。如果用XY坐標平面表示,則乘法器有四個可能的工作區,即四個工作象限,如圖。

若信號均限定為某一極性的電壓時才能正常工作,該乘法器稱為單象限乘法器;若信號中一個能適應正、負兩種極性電壓,而另一個只能適應單極性電壓,則為二象限乘法器;若兩個輸入信號能適應四種極性組合,稱為四象限乘法器。

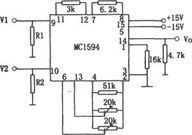

集成模擬乘法器的常見產品有BG314、F1595、F1596、MC1495、MC1496、LM1595、LM1596等。

硬體乘法器

硬體乘法器,其基礎就是加法器結構,它已經是現代計算機中必不可少的一部分。乘法器的模型就是基於“移位和相加”的算法。在該算法中,乘法器中每一個比特位都會產生一個局部乘積。第一個局部乘積由乘法器的LSB產生,第二個乘積由乘法器的第二位產生,以此類推。如果相應的乘數比特位是1,那么局部乘積就是被乘數的值,如果相應的乘數比特位是0,那么局部乘積全為0。每次局部乘積都向左移動一位。

乘法器可以用更普遍的方式來表示。每個輸入,局部乘積數,以及結果都被賦予了一個邏輯名稱(如A1、A2、B1、B2),而這些名稱在電路原理圖中就作為了信號名稱。在原理圖的乘法例子中比較信號名稱,就可以找到乘法電路的行為特性。

在乘法器電路中,乘數中的每一位都要和被乘數的每一位相與,並產生其相應的乘積位。這些局部乘積要饋入到全加器的陣列中(合適的時候也可以用半加器),同時加法器向左移位並表示出乘法結果。最後得到的乘積項在CLA電路中相加。注意,某些全加器電路會將信號帶入到進位輸入端(用於替代鄰近位的進位)。這就是一種全加器電路的套用;全加器將其輸入端的任何三個比特相加。

隨著乘數和被乘數位數的增加,乘法器電路中的加法器位數也要相應的增加。通過研究CLA電路的特性,也可以在乘法器中開發出更快的加法陣列。