歷史發展

eda

eda在電子設計自動化(英語:Electronic design automation,縮寫:EDA)出現之前,設計人員必須手工完成積體電路的設計、布線等工作,這是因為當時所謂積體電路的複雜程度遠不及現在。工業界開始使用幾何學方法來製造用於電路光繪(photoplotter)的膠帶。到了1970年代中期,開發人應嘗試將整個設計過程自動化,而不僅僅滿足於自動完成掩膜草圖。第一個電路布線、布局工具研發成功。設計自動化會議(Design Automation Conference)在這一時期被創立,旨在促進電子設計自動化的發展。

電子設計自動化發展的下一個重要階段以卡弗爾·米德(Carver Mead)和琳·康維於1980年發表的論文《超大規模積體電路系統導論》(Introduction to VLSI Systems)為標誌。這一篇具有重大意義的論文提出了通過程式語言來進行晶片設計的新思想。如果這一想法得到實現,晶片設計的複雜程度可以得到顯著提升。這主要得益於用來進行積體電路邏輯仿真、功能驗證的工具的性能得到相當的改善。隨著計算機仿真技術的發展,設計項目可以在構建實際硬體電路之前進行仿真,晶片布線布局對人工設計的要求降低,而且軟體錯誤率不斷降低。直至今日,儘管所用的語言和工具仍然不斷在發展,但是通過程式語言來設計、驗證電路預期行為,利用工具軟體綜合得到低抽象級物理設計的這種途徑,仍然是數字積體電路設計的基礎。

從1981年開始,電子設計自動化逐漸開始商業化。1984年的設計自動化會議(Design Automation Conference)上還舉辦了第一個以電子設計自動化為主題的銷售展覽。Gateway設計自動化在1986年推出了一種硬體描述語言Verilog,這種語言在現在是最流行的高級抽象設計語言。1987年,在美國國防部的資助下,另一種硬體描述語言VHDL被創造出來。現代的電子設計自動化設計工具可以識別、讀取不同類型的硬體描述。根據這些語言規範產生的各種仿真系統迅速被推出,使得設計人員可對設計的晶片進行直接仿真。後來,技術的發展更側重於邏輯綜合。

目前的數字積體電路的設計都比較模組化(參見積體電路設計、設計收斂(Design closure)和設計流(Design flow (EDA)))。半導體器件製造工藝需要標準化的設計描述,高抽象級的描述將被編譯為信息單元(cell)的形式。設計人員在進行邏輯設計時尚無需考慮信息單元的具體硬體工藝。利用特定的積體電路製造工藝來實現硬體電路,信息單元就會實施預定義的邏輯或其他電子功能。半導體硬體廠商大多會為它們製造的元件提供“元件庫”,並提供相應的標準化仿真模型。相比數字的電子設計自動化工具,模擬系統的電子設計自動化工具大多並非模組化的,這是因為模擬電路的功能更加複雜,而且不同部分的相互影響較強,而且作用規律複雜,電子元件大多沒有那么理想。Verilog AMS就是一種用於模擬電子設計的硬體描述語言。此文,設計人員可以使用硬體驗證語言來完成項目的驗證工作目前最新的發展趨勢是將集描述語言、驗證語言集成為一體,典型的例子有SystemVerilog。

隨著積體電路規模的擴大、半導體技術的發展,電子設計自動化的重要性急劇增加。這些工具的使用者包括半導體器件製造中心的硬體技術人員,他們的工作是操作半導體器件製造設備並管理整個工作車間。一些以設計為主要業務的公司,也會使用電子設計自動化軟體來評估製造部門是否能夠適應新的設計任務。電子設計自動化工具還被用來將設計的功能導入到類似現場可程式邏輯門陣列的半定製可程式邏輯器件,或者生產全定製的專用積體電路。

概念

EDA技術的概念

EDA技術是指以計算機為工作平台,融合了套用電子技術、計算機技術、信息處理及智慧型化技術的最新成果,進行電子產品的自動設計。

利用EDA工具,電子設計師可以從概念、算法、協定等開始設計電子系統,大量工作可以通過計算機完成,並可以將電子產品從電路設計、性能分析到設計出IC版圖或PCB版圖的整個過程的計算機上自動處理完成。

套用

現在對EDA的概念或範疇用得很寬。包括在機械、電子、通信、航空航天、化工、礦產、生物、醫學、軍事等各個領域,都有EDA的套用。目前EDA技術已在各大公司、企事業單位和科研教學部門廣泛使用。例如在飛機製造過程中,從設計、性能測試及特性分析直到飛行模擬,都可能涉及到EDA技術。本文所指的EDA技術,主要針對電子電路設計、PCB設計和IC設計。

EDA設計可分為系統級、電路級和物理實現級。

設計方法

eda

eda(1) 前端設計(系統建模RTL 級描述)後端設計(FPGAASIC)系統建模

(2) IP 復用

(3) 前端設計

(4) 系統描述:建立系統的數學模型。

(5) 功能描述:描述系統的行為或各子模組之間的數據流圖。

(6) 邏輯設計:將系統功能結構化,通常以文本、原理圖、邏輯圖、布爾表達式來表示設計結果。

(7) 仿真:包括功能仿真和時序仿真,主要驗證系統功能的正確性及時序特性。

設計技巧

eda

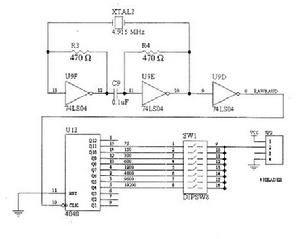

eda(1)密碼鎖輸入電路KEYB 0ARD.VHD中對各種分頻信號/信號序列的設計有獨到之處。該設計中,利用一個自由計數器來產生各種需要的頻率,也就是先建立一個N位計數器,N的大小根據電路的需求決定。N的值越大,電路可以除頻的次數就越多,這樣就可以獲得更大的頻率變化,以便提供多種不同頻率的時鐘信號。若輸入時鐘為CLK,N位計數器的輸出為Q[N-1,0],則Q(0)為CLK的2分頻脈衝信號,Q(1)為CLK的4分頻脈衝信號,Q(2)為CLK的8分頻脈衝信號,……Q(N-1)為CLK的2N分頻脈衝信號;Q(5 DOWNT04)取得的是一個脈衝波形序列,其值是依00、01、10、11、00、01周期性變化的,其變化頻率為CLK的25分頻,也就是32分頻。我們利用以上規律即可得到各種我們所需要頻率的信號或信號序列。

(2)鍵盤輸入去抖電路的設計程式DEBOUNCING.VHD在實際系統的開發中有較好的參考價值。

(3)密碼鎖控制電路CTRL,VHD中對於數據的更新及移位方法比較好。程式中使用語句“ACC <=ACC(11 DOWNT0 0)&DATA_N”非常簡潔地同時實現了ACC中的低4位用DATA_N進行更新,而高12位用ACC中的原來的低12位左移而來的處理。

(4)在密碼鎖輸入電路等模組的程式的設計和仿真中,為了便於觀察一些中間結果,在程式中增加了一些觀測輸出點。這一設計技巧,對於較大的程式或多進程程式的設計非常重要。同時在仿真時,為了便於觀測全局結果,降低了分頻常數。同理,在進行程式仿真時,對於程式中數目較大的分頻/計數/計時常數的修改是非常必要的。

工具軟體

EDA工具軟體可大致可分為晶片設計輔助軟體、可程式晶片輔助設計軟體、系統設計輔助軟體等三類。

目前進入我國並具有廣泛影響的EDA軟體是系統設計軟體輔助類和可程式晶片輔助設計軟體:Protel、PSPICE、multiSIM7(原EWB的最新版本)、OrCAD、PCAD、、LSIIogic、MicroSim,ISE,modelsim等等。這些工具都有較強的功能,一般可用於幾個方面,例如很多軟體都可以進行電路設計與仿真,同進還可以進行PCB自動布局布線,可輸出多種網表檔案與第三方軟體接口。

EDA工具軟體廠商三巨頭:Synopsys、Mentor Graphics、Cadence。

電子電路設計與仿真工具

eda

eda我們大家可能都用過試驗板或者其他的東西製作過一些電子製做來進行實踐。但是有的時候,我們會發現做出來的東西有很多的問題,事先並沒有想到,這樣一來就浪費了我們的很多時間和物資。而且增加了產品的開發周期和延續了產品的上市時間從而使產品失去市場競爭優勢。有沒有能夠不動用電烙鐵試驗板就能知道結果的方法呢?結論是有,這就是電路設計與仿真技術。

說到電子電路設計與仿真工具這項技術,就不能不提到美國,不能不提到他們的飛機設計為什麼有很高的效率。以前我國定型一個中型飛機的設計,從草案到詳細設計到風洞試驗再到最後出圖到實際投產,整個周期大概要10年。而美國是1年。為什麼會有這樣大的差距呢?因為美國在設計時大部分採用的是虛擬仿真技術,把多年積累的各項風洞實驗參數都輸入電腦,然後通過電腦編程編寫出一個虛擬環境的軟體,並且使它能夠自動套用相關公式和調用長期積累後輸入電腦的相關經驗參數。這樣一來,只要把飛機的外形計數據放入這個虛擬的風洞軟體中進行試驗,哪裡不合理有問題就改動那裡,直至最佳效果,效率自然高了,最後只要再在實際環境中測試幾次找找不足就可以定型了,從他們的波音747到F16都是採用的這種方法。空氣動力學方面的數據由資深專家提供,軟體開發商是IBM,飛行器設計工程師只需利用仿真軟體在計算機平台上進行各種仿真調試工作即可。同樣,他們其他的很多東西都是採用了這樣類似的方法,從大到小,從複雜到簡單,甚至包括設計家具和作曲,只是具體軟體內容不同。其實,他們發明第一代計算機時就是這個目的(當初是為了高效率設計大炮和相關炮彈以及其他計算量大的設計)。

電子電路設計與仿真工具包括SPICE/PSPICE;multiSIM7;Matlab;SystemView;MMICAD LiveWire、Edison、Tina Pro Bright Spark等。下面簡單介紹前三個軟體。

①SPICE(Simulation Program with Integrated Circuit Emphasis):是由美國加州大學推出的電路分析仿真軟體,是20世紀80年代世界上套用最廣的電路設計軟體,1998年被定為美國國家標準。1984年,美國MicroSim公司推出了基於SPICE的微機版PSPICE(Personal-SPICE)。現在用得較多的是PSPICE6.2,可以說在同類產品中,它是功能最為強大的模擬和數字電路混合仿真EDA軟體,在國內普遍使用。最新推出了PSPICE9.1版本。它可以進行各種各樣的電路仿真、激勵建立、溫度與噪聲分析、模擬控制、波形輸出、數據輸出、並在同一視窗內同時顯示模擬與數字的仿真結果。無論對哪種器件哪些電路進行仿真,都可以得到精確的仿真結果,並可以自行建立元器件及元器件庫。

②multiSIM(EWB的最新版本)軟體:是Interactive Image Technologies Ltd在20世紀末推出的電路仿真軟體。其最新版本為multiSIM7,目前普遍使用的是multiSIM2001,相對於其它EDA軟體,它具有更加形象直觀的人機互動界面,特別是其儀器儀表庫中的各儀器儀表與操作真實實驗中的實際儀器儀表完全沒有兩樣,但它對模數電路的混合仿真功能卻毫不遜色,幾乎能夠100%地仿真出真實電路的結果,並且它在儀器儀表庫中還提供了萬用表、信號發生器、瓦特表、雙蹤示波器(對於multiSIM7還具有四蹤示波器)、波特儀(相當實際中的掃頻儀)、字信號發生器、邏輯分析儀、邏輯轉換儀、失真度分析儀、頻譜分析儀、網路分析儀和電壓表及電流表等儀器儀表。還提供了我們日常常見的各種建模精確的元器件,比如電阻、電容、電感、三極體、二極體、繼電器、可控矽、數碼管等等。模擬積體電路方面有各種運算放大器、其他常用積體電路。數字電路方面有74系列積體電路、4000系列積體電路、等等還支持自製元器件。MultiSIM7還具有I-V分析儀(相當於真實環境中的電晶體特性圖示儀)和Agilent信號發生器、Agilent萬用表、Agilent示波器和動態邏輯平筆等。同時它還能進行VHDL仿真和Verilog HDL仿真。

③MATLAB產品族:它們的一大特性是有眾多的面向具體套用的工具箱和仿真塊,包含了完整的函式集用來對圖像信號處理、控制系統設計、神經網路等特殊套用進行分析和設計。它具有數據採集、報告生成和MATLAB語言編程產生獨立C/C++代碼等功能。MATLAB產品族具有下列功能:數據分析;數值和符號計算、工程與科學繪圖;控制系統設計;數字圖像信號處理;財務工程;建模、仿真、原型開發;套用開發;圖形用戶界面設計等。MATLAB產品族被廣泛套用於信號與圖像處理、控制系統設計、通訊系統仿真等諸多領域。開放式的結構使MATLAB產品族很容易針對特定的需求進行擴充,從而在不斷深化對問題的認識同時,提高自身的競爭力。

PCB設計軟體

PCB(Printed-Circuit Board)設計軟體種類很多,如Protel、Altium Designer、OrCAD、Viewlogic、PowerPCB、Cadence PSD、MentorGraphices的Expedition PCB、Zuken CadStart、Winboard/Windraft/Ivex-SPICE、PCB Studio、TANGO、PCBWizard(與LiveWire配套的PCB製作軟體包)、ultiBOARD7(與multiSIM2001配套的PCB製作軟體包)等等。

目前在我國用得最多當屬Protel,下面僅對此軟體作一介紹。

Protel是PROTEL(現為Altium)公司在20世紀80年代末推出的CAD工具,是PCB設計者的首選軟體。它較早在國內使用,普及率最高,在很多的大、中專院校的電路專業還專門開設Protel課程,幾乎所在的電路公司都要用到它。早期的Protel主要作為印刷板自動布線工具使用,其最新版本為Altium Designer 10,現在普遍使用的是Protel99SE,它是個完整的全方位電路設計系統,包含了電原理圖繪製、模擬電路與數字電路混合信號仿真、多層印刷電路板設計(包含印刷電路板自動布局布線),可程式邏輯器件設計、圖表生成、電路表格生成、支持宏操作等功能,並具有Client/Server(客戶/服務體系結構), 同時還兼容一些其它設計軟體的檔案格式,如ORCAD、PSPICE、EXCEL等。使用多層印製線路板的自動布線,可實現高密度PCB的100%布通率。Protel軟體功能強大(同時具有電路仿真功能和PLD開發功能)、界面友好、使用方便,但它最具代表性的是電路設計和PCB設計。

IC設計軟體

IC設計工具很多,其中按市場所占份額排行為Cadence、Mentor Graphics和Synopsys。這三家都是ASIC設計領域相當有名的軟體供應商。其它公司的軟體相對來說使用者較少。中國華大公司也提供ASIC設計軟體(熊貓2000);另外近來出名的Avanti公司,是原來在Cadence的幾個華人工程師創立的,他們的設計工具可以全面和Cadence公司的工具相抗衡,非常適用於深亞微米的IC設計。下面按用途對IC設計軟體作一些介紹。

①設計輸入工具

這是任何一種EDA軟體必須具備的基本功能。像Cadence的composer,viewlogic的viewdraw,硬體描述語言VHDL、Verilog HDL是主要設計語言,許多設計輸入工具都支持HDL(比如說multiSIM等)。另外像Active-HDL和其它的設計輸入方法,包括原理和狀態機輸入方法,設計FPGA/CPLD的工具大都可作為IC設計的輸入手段,如Xilinx、Altera等公司提供的開發工具Modelsim FPGA等。

②設計仿真工作

我們使用EDA工具的一個最大好處是可以驗證設計是否正確,幾乎每個公司的EDA產品都有仿真工具。Verilog-XL、NC-verilog用於Verilog仿真,Leapfrog用於VHDL仿真,Analog Artist用於模擬電路仿真。Viewlogic的仿真器有:viewsim門級電路仿真器,speedwaveVHDL仿真器,VCS-verilog仿真器。Mentor Graphics有其子公司Model Tech出品的VHDL和Verilog雙仿真器:Model Sim。Cadence、Synopsys用的是VSS(VHDL仿真器)。現在的趨勢是各大EDA公司都逐漸用HDL仿真器作為電路驗證的工具。

③綜合工具

綜合工具可以把HDL變成門級網表。這方面Synopsys工具占有較大的優勢,它的Design Compile是作為一個綜合的工業標準,它還有另外一個產品叫Behavior Compiler,可以提供更高級的綜合。

另外最近美國又出了一個軟體叫Ambit,據說比Synopsys的軟體更有效,可以綜合50萬門的電路,速度更快。今年初Ambit被Cadence公司收購,為此Cadence放棄了它原來的綜合軟體Synergy。隨著FPGA設計的規模越來越大,各EDA公司又開發了用於FPGA設計的綜合軟體,比較有名的有:Synopsys的FPGA Express, Cadence的Synplity, Mentor的Leonardo,這三家的FPGA綜合軟體占了市場的絕大部分。

④布局和布線

在IC設計的布局布線工具中,Cadence軟體是比較強的,它有很多產品,用於標準單元、門陣列已可實現互動布線。最有名的是Cadence spectra,它原來是用於PCB布線的,後來Cadence把它用來作IC的布線。其主要工具有:Cell3,Silicon Ensemble-標準單元布線器;Gate Ensemble-門陣列布線器;Design Planner-布局工具。其它各EDA軟體開發公司也提供各自的布局布線工具。

⑤物理驗證工具

物理驗證工具包括版圖設計工具、版圖驗證工具、版圖提取工具等等。這方面Cadence也是很強的,其Dracula、Virtuso、Vampire等物理工具有很多的使用者。

⑥模擬電路仿真器

前面講的仿真器主要是針對數字電路的,對於模擬電路的仿真工具,普遍使用SPICE,這是唯一的選擇。只不過是選擇不同公司的SPICE,像MiceoSim的PSPICE、Meta Soft的HSPICE等等。HSPICE現在被Avanti公司收購了。在眾多的SPICE中,HSPICE作為IC設計,其模型多,仿真的精度也高。

PLD設計工具

PLD(Programmable Logic Device)是一種由用戶根據需要而自行構造邏輯功能的數字積體電路。目前主要有兩大類型:CPLD(Complex PLD)和FPGA(Field Programmable Gate Array)。它們的基本設計方法是藉助於EDA軟體,用原理圖、狀態機、布爾表達式、硬體描述語言等方法,生成相應的目標檔案,最後用編程器或下載電纜,由目標器件實現。生產PLD的廠家很多,但最有代表性的PLD廠家為Altera、Xilinx和Lattice公司。

PLD的開發工具一般由器件生產廠家提供,但隨著器件規模的不斷增加,軟體的複雜性也隨之提高,目前由專門的軟體公司與器件生產廠家使用,推出功能強大的設計軟體。下面介紹主要器件生產廠家和開發工具。

①ALTERA:20世紀90年代以後發展很快。主要產品有:MAX3000/7000、FELX6K/10K、APEX20K、ACEX1K、Stratix等。其開發工具-MAX+PLUS II是較成功的PLD開發平台,最新又推出了Quartus II開發軟體。Altera公司提供較多形式的設計輸入手段,綁定第三方VHDL綜合工具,如:綜合軟體FPGA Express、Leonard Spectrum,仿真軟體ModelSim。

②XILINX:FPGA的發明者。產品種類較全,主要有:XC9500/4000、Coolrunner(XPLA3)、Spartan、Vertex等系列,其最大的Vertex-II Pro器件已達到800萬門。開發軟體為Foundation和ISE。通常來說,在歐洲用Xilinx的人多,在日本和亞太地區用ALTERA的人多,在美國則是平分秋色。全球PLD/FPGA產品60%以上是由Altera和Xilinx提供的。可以講Altera和Xilinx共同決定了PLD技術的發展方向。

③Lattice-Vantis:Lattice是ISP(In-System Programmability)技術的發明者。ISP技術極大地促進了PLD產品的發展,與ALTERA和XILINX相比,其開發工具比Altera和Xilinx略遜一籌。中小規模PLD比較有特色,大規模PLD的競爭力還不夠強(Lattice沒有基於查找表技術的大規模FPGA),1999年推出可程式模擬器件,1999年收購Vantis(原AMD子公司),成為第三大可程式邏輯器件供應商。2001年12月收購Agere公司(原Lucent微電子部)的FPGA部門。主要產品有ispLSI2000/5000/8000,MACH4/5。

④ACTEL:反熔絲(一次性燒寫)PLD的領導者。由於反熔絲PLD抗輻射、耐高低溫、功耗低、速度快,所以在軍品和宇航級上有較大優勢。ALTERA和XILINX則一般不涉足軍品和宇航級市場。

⑤Quicklogic:專業PLD/FPGA公司,以一次性反熔絲工藝為主,在中國地區銷售量不大。

⑥Lucent:主要特點是有不少用於通訊領域的專用IP核,但PLD/FPGA不是Lucent的主要業務,在中國地區使用的人很少。

⑦ATMEL:中小規模PLD做得不錯。ATMEL也做了一些與Altera和Xilinx兼容的片子,但在品質上與原廠家還是有一些差距,在高可靠性產品中使用較少,多用在低端產品上。

⑧Clear Logic:生產與一些著名PLD/FPGA大公司兼容的晶片,這種晶片可將用戶的設計一次性固化,不可程式,批量生產時的成本較低。

⑨WSI:生產PSD(單片機可程式外圍晶片)產品。這是一種特殊的PLD,如最新的PSD8xx、PSD9xx集成了PLD、EPROM、Flash,並支持ISP(線上編程),集成度高,主要用於配合單片機工作。

⑦Altium:提供Actel、Altera、Lattice和Xilinx四家PLD/FPGA器件的通用跨廠商開發平台,最新推出了Altium Designer 10 軟體中集成了Aldec HDL仿真功能。

順便提一下:PLD(可程式邏輯器件)是一種可以完全替代74系列及GAL、PLA的新型電路,只要有數字電路基礎,會使用計算機,就可以進行PLD的開發。PLD的線上編程能力和強大的開發軟體,使工程師可以幾天,甚至幾分鐘內就可完成以往幾周才能完成的工作,並可將數百萬門的複雜設計集成在一顆晶片內。PLD技術在已開發國家已成為電子工程師必備的技術。

其它EDA軟體

①VHDL語言:超高速積體電路硬體描述語言(VHSIC Hardware Deseription Languagt,簡稱VHDL),是IEEE的一項標準設計語言。它源於美國國防部提出的超高速積體電路(Very High Speed Integrated Circuit,簡稱VHSIC)計畫,是ASIC設計和PLD設計的一種主要輸入工具。

②Veriolg HDL:是Verilog公司推出的硬體描述語言,在ASIC設計方面與VHDL語言平分秋色。

③其它EDA軟體如專門用於微波電路設計和電力載波工具、PCB製作和工藝流程控制等領域的工具,在此就不作介紹了。

工具套用

EDA在教學、科研、產品設計與製造等各方面都發揮著巨大的作用。在教學方面,幾乎所有理工科(特別是電子信息)類的高校都開設了EDA課程。主要是讓學生了解EDA的基本概念和基本原理、掌握用HDL語言編寫規範、掌握邏輯綜合的理論和算法、使用EDA工具進行電子電路課程的實驗驗證並從事簡單系統的設計。一般學習電路仿真工具(如multiSIM、PSPICE)和PLD開發工具(如Altera/Xilinx的器件結構及開發系統),為今後工作打下基礎。

科研方面主要利用電路仿真工具(multiSIM或PSPICE)進行電路設計與仿真;利用虛擬儀器進行產品測試;將CPLD/FPGA器件實際套用到儀器設備中;從事PCB設計和ASIC設計等。

在產品設計與製造方面,包括計算機仿真,產品開發中的EDA工具套用、系統級模擬及測試環境的仿真,生產流水線的EDA技術套用、產品測試等各個環節。如PCB的製作、電子設備的研製與生產、電路板的焊接、ASIC的製作過程等。

從套用領域來看,EDA技術已經滲透到各行各業,如上文所說,包括在機械、電子、通信、航空航航天、化工、礦產、生物、醫學、軍事等各個領域,都有EDA套用。另外,EDA軟體的功能日益強大,原來功能比較單一的軟體,現在增加了很多新用途。如AutoCAD軟體可用於機械及建築設計,也擴展到建築裝璜及各類效果圖、汽車和飛機的模型、電影特技等領域。

發展趨勢

從目前的EDA技術來看,其發展趨勢是政府重視、使用普及、套用廣泛、工具多樣、軟體功能強大。

中國EDA市場已漸趨成熟,不過大部分設計工程師面向的是PCB制板和小型ASIC領域,僅有小部分(約11%)的設計人員開發複雜的片上系統器件。為了與台灣和美國的設計工程師形成更有力的競爭,中國的設計隊伍有必要引進和學習一些最新的EDA技術。

在信息通信領域,要優先發展高速寬頻信息網、深亞微米積體電路、新型元器件、計算機及軟體技術、第三代移動通信技術、信息管理、信息安全技術,積極開拓以數位技術、網路技術為基礎的新一代信息產品,發展新興產業,培育新的經濟成長點。要大力推進制造業信息化,積極開展計算機輔助設計(CAD)、計算機輔助工程(CAE)、計算機輔助工藝(CAPP)、計算機機輔助製造(CAM)、產品數據管理(PDM)、製造資源計畫(MRPII)及企業資源管理(ERP)等。有條件的企業可開展“網路製造”,便於合作設計、合作製造,參與國內和國際競爭。開展“數控化”工程和“數位化”工程。自動化儀表的技術發展趨勢的測試技術、控制技術與計算機技術、通信技術進一步融合,形成測量、控制、通信與計算機(M3C)結構。在ASIC和PLD設計方面,向超高速、高密度、低功耗、低電壓方面發展。

外設技術與EDA工程相結合的市場前景看好,如組合超大螢幕的相關連線,多螢幕技術也有所發展。

中國自1995年以來加速開發半導體產業,先後建立了幾所設計中心,推動系列設計活動以應對亞太地區其它EDA市場的競爭。

在EDA軟體開發方面,目前主要集中在美國。但各國也正在努力開發相應的工具。日本、韓國都有ASIC設計工具,但不對外開放。中國華大積體電路設計中心,也提供IC設計軟體,但性能不是很強。相信在不久的將來會有更多更好的設計工具在各地開花並結果。據最新統計顯示,中國和印度正在成為電子設計自動化領域發展最快的兩個市場,年夏合增長率分別達到了50%和30%。

廠商巨頭

eda

edaSynopsys、Mentor、Cadence。

PADS(Personal Automated Design Systems個人自動設計系統)軟體是美國Mentor Graphics公司的產品。PowerLogic5.0是一個功能強大、多頁的原理圖設計輸入工具,具有在每頁進行快速存取、線上元件編輯、庫管理方便簡潔等特點,所有這些都為PowerPCB提供了高效的電路板設計環境,提高了由原理圖設計連結到PCB製版的轉化效率。 PowerPCB 5.0是一個複雜的、高速印製電路板設計軟體。它具有快速互動布線編輯器(FIRE),它的這一功能在眾多的互動布線模式中獨樹一幟,由於FIRE採用強大功能的算法,布線完成後很少需要用戶修改調整,可以使用戶在布線時節省大量時間,提高效率。對表貼元件等細小焊盤間距、對高速布線的約束條件設定、對圖形用戶界面的定製等方面功能,PowerPCB5.0軟體都是無可挑剔的。由於PowerLogic5.0和PowerPCB5.0兩軟體運行速度快,加之功能強大,有些簡單的操作可以實現複雜的功能、快捷鍵方便、視窗寬等優點。

化學製劑

化學eda

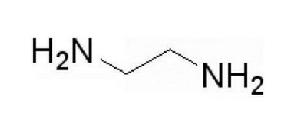

化學eda乙二胺Ethylene diamine(EDA), or1,2-diaminoethane, is anorganic compoundfrom theaminesgroup. Its formula is H2N-CH2CH2-NH2. It is a stronglyalkaline, colorless to yellowish liquid, with amine odor, completelymisciblewith water and soluble inalcohol. Its melting point is 8.5°C and boiling point 116°C. ItsCAS reference numberis 107-15-3.

乙二胺(EDA), 或二氨基乙烷,是一種胺類有機化合物。其分子式為H2N-CH2CH2-NH2.乙二胺是一種強鹼,無色至微黃色液體,帶有胺氣味,完全溶於水並可溶於酒精。熔點8.5°C 、沸點116°C。引自《化學文摘社》編號107-15-3。

分布估算

分布估算法

分布估算法分布估計算法EDA(Estimation of Distribution Algorithms)是進化計算領域新興起的一類隨機最佳化算法,當前國際進化計算領域的研究熱點. 它是遺傳算法和統計學習的結合,通過統計學習的手段建立解空間內個體分布的機率模型,然後對機率模型隨機採樣產生新的群體,如此反覆進行,實現群體的進化. 分布估計算法中沒有傳統的交叉、變異等遺傳操作,是一種全新的進化模式;這種最佳化技術能夠通過機率圖模型對變數之間的關係進行建模,從而能有效的解決多變數相關的最佳化問題.

“eda”在英漢詞典中的解釋(來源:百度詞典):

EDA abbr. 1. =Economic Development Administration (美國)(商務部)經濟開發署 2. =Economic Development Association (美國)經濟開發協會

eda abbr. 1. =early departure authorized 經批准提前出發

疑問解答

1-1 EDA技術與ASIC設計和FPGA開發有什麼關係?

答:利用EDA技術進行電子系統設計的最後目標是完成專用積體電路ASIC的設計和實現;FPGA和CPLD是實現這一途徑的主流器件。FPGA和CPLD通常也被稱為可程式專用IC,或可程式ASIC。FPGA和CPLD的套用是EDA技術有機融合軟硬體電子設計技術、SoC(片上系統)和ASIC設計,以及對自動設計與自動實現最典型的詮釋。

1-2與軟體描述語言相比,VHDL有什麼特點?

答:編譯器將軟體程式翻譯成基於某種特定CPU的機器代碼,這種代碼僅限於這種CPU而不能移植,並且機器代碼不代表硬體結構,更不能改變CPU的硬體結構,只能被動地為其特定的硬體電路結構所利用。綜合器將VHDL程式轉化的目標是底層的電路結構網表檔案,這種滿足VHDL設計程式功能描述的電路結構,不依賴於任何特定硬體環境;具有相對獨立性。綜合器在將VHDL(硬體描述語言)表達的電路功能轉化成具體的電路結構網表過程中,具有明顯的能動性和創造性,它不是機械的一一對應式的“翻譯”,而是根據設計庫、工藝庫以及預先設定的各類約束條件,選擇最優的方式完成電路結構的設計。

l-3什麼是綜合?有哪些類型?綜合在電子設計自動化中的地位是什麼?

什麼是綜合?答:在電子設計領域中綜合的概念可以表示為:將用行為和功能層次表達的電子系統轉換為低層次的便於具體實現的模組組合裝配的過程。

有哪些類型? 答:(1)從自然語言轉換到VHDL語言算法表示,即自然語言綜合。(2)從算法表示轉換到暫存器傳輸級(RegisterTransport Level,RTL),即從行為域到結構域的綜合,即行為綜合。(3)從RTL級表示轉換到邏輯門(包括觸發器)的表示,即邏輯綜合。(4)從邏輯門表示轉換到版圖表示(ASIC設計),或轉換到FPGA的配置網表檔案,可稱為版圖綜合或結構綜合。

綜合在電子設計自動化中的地位是什麼? 答:是核心地位(見圖1-3)。綜合器具有更複雜的工作環境,綜合器在接受VHDL程式並準備對其綜合前,必須獲得與最終實現設計電路硬體特徵相關的工藝庫信息,以及獲得最佳化綜合的諸多約束條件信息;根據工藝庫和約束條件信息,將VHDL程式轉化成電路實現的相關信息。

1-4在EDA技術中,自頂向下的設計方法的重要意義是什麼? P7~10

答:在EDA技術套用中,自頂向下的設計方法,就是在整個設計流程中各設計環節逐步求精的過程。

1-5 IP在EDA技術的套用和發展中的意義是什麼?P11~12

答:IP核具有規範的接口協定,良好的可移植與可測試性,為系統開發提供了可靠的保證。

2-1 敘述EDA的FPGA/CPLD設計流程。P13~16

答:1.設計輸入(原理圖/HDL文本編輯);2.綜合;3.適配;4.時序仿真與功能仿真;5.編程下載;6.硬體測試。

2-2 IP是什麼?IP與EDA技術的關係是什麼?P24~26

IP是什麼?答:IP是智慧財產權核或智慧財產權模組,用於ASIC或FPGA/CPLD中的預先設計好的電路功能模組。

IP與EDA技術的關係是什麼? 答:IP在EDA技術開發中具有十分重要的地位;與EDA技術的關係分有軟IP、固IP、硬IP:軟IP是用VHDL等硬體描述語言描述的功能塊,並不涉及用什麼具體電路元件實現這些功能;軟IP通常是以硬體描述語言HDL源檔案的形式出現。固IP是完成了綜合的功能塊,具有較大的設計深度,以網表檔案的形式提交客戶使用。硬IP提供設計的最終階段產品:掩模。

2-3 敘述ASIC的設計方法。 P18~19

答:ASIC設計方法,按版圖結構及製造方法分有半定製(Semi-custom)和全定製(Full-custom)兩種實現方法。

全定製方法是一種基於電晶體級的,手工設計版圖的製造方法。

半定製法是一種約束性設計方式,約束的目的是簡化設計,縮短設計周期,降低設計成本,提高設計正確率。半定製法按邏輯實現的方式不同,可再分為門陣列法、標準單元法和可程式邏輯器件法。

2-4 FPGA/CPLD在ASIC設計中有什麼用途?P16,18

答:FPGA/CPLD在ASIC設計中,屬於可程式ASIC的邏輯器件;使設計效率大為提高,上市的時間大為縮短。

2-5 簡述在基於FPGA/CPLD的EDA設計流程中所涉及的EDA工具,及其在整個流程中的作用。 P19~23

答:基於FPGA/CPLD的EDA設計流程中所涉及的EDA工具有:設計輸入編輯器(作用:接受不同的設計輸入表達方式,如原理圖輸入方式、狀態圖輸入方式、波形輸入方式以及HDL的文本輸入方式。);HDL綜合器(作用:HDL綜合器根據工藝庫和約束條件信息,將設計輸入編輯器提供的信息轉化為目標器件硬體結構細節的信息,並在數字電路設計技術、化簡最佳化算法以及計算機軟體等複雜結體進行最佳化處理);仿真器(作用:行為模型的表達、電子系統的建模、邏輯電路的驗證及門級系統的測試);適配器(作用:完成目標系統在器件上的布局和布線);下載器(作用:把設計結果信息下載到對應的實際器件,實現硬體設計)。

3-1 OLMC(輸出邏輯宏單元)有何功能?說明GAL是怎樣實現可程式組合電路與時序電路的。 P34~36

OLMC有何功能?答:OLMC單元設有多種組態,可配置成專用組合輸出、專用輸入、組合輸出雙向口、暫存器輸出、暫存器輸出雙向口等。

說明GAL是怎樣實現可程式組合電路與時序電路的? 答:GAL(通用陣列邏輯器件)是通過對其中的OLMC(輸出邏輯宏單元)的編程和三種模式配置(暫存器模式、複合模式、簡單模式),實現組合電路與時序電路設計的。

3-2什麼是基於乘積項的可程式邏輯結構?P33~34,40

答:GAL、CPLD之類都是基於乘積項的可程式結構;即包含有可程式與陣列和固定的或陣列的PAL(可程式陣列邏輯)器件構成。

3-3什麼是基於查找表的可程式邏輯結構?P40~41

答:FPGA(現場可程式門陣列)是基於查找表的可程式邏輯結構。

3-4 FPGA系列器件中的LAB有何作用? P43~45

答:FPGA(Cyclone/Cyclone II)系列器件主要由邏輯陣列塊LAB、嵌入式存儲器塊(EAB)、I/O單元、嵌入式硬體乘法器和PLL等模組構成;其中LAB(邏輯陣列塊)由一系列相鄰的LE(邏輯單元)構成的;FPGA可程式資源主要來自邏輯陣列塊LAB。

3-5與傳統的測試技術相比,邊界掃描技術有何優點?P47~50

答:使用BST(邊界掃描測試)規範測試,不必使用物理探針,可在器件正常工作時在系統捕獲測量的功能數據。克服傳統的外探針測試法和“針床”夾具測試法來無法對IC內部節點無法測試的難題。

3-6解釋編程與配置這兩個概念。P58

答:編程:基於電可擦除存儲單元的EEPROM或Flash技術。CPLD一股使用此技術進行編程。CPLD被編程後改變了電可擦除存儲單元中的信息,掉電後可保存。電可擦除編程工藝的優點是編程後信息不會因掉電而丟失,但編程次數有限,編程的速度不快。

配置:基於SRAM查找表的編程單元。編程信息是保存在SRAM中的,SRAM在掉電後編程信息立即丟失,在下次上電後,還需要重新載入編程信息。大部分FPGA採用該種編程工藝。該類器件的編程一般稱為配置。對於SRAM型FPGA來說,配置次數無限,且速度快;在加電時可隨時更改邏輯;下載信息的保密性也不如電可擦除的編程。

3-7請參閱相關資料,並回答問題:按本章給出的歸類方式,將基於乘積項的可程式邏輯結構的PLD器件歸類為CPLD;將基於查找表的可程式邏輯結構的PLD器什歸類為FPGA,那么,APEX系列屬於什麼類型PLD器件?MAX II系列又屬於什麼類型的PLD器件?為什麼?P54~56

答:APEX(Advanced Logic Element Matrix)系列屬於FPGA類型PLD器件;編程信息存於SRAM中。MAX II系列屬於CPLD類型的PLD器件;編程信息存於EEPROM中。

幾個有關EDA的專題網站

EDA中心 www.eda.ac.cn

中國EDA技術網 www.51eda.com

EDA愛好者 www.edafans.com

EDA教學與研究 www.edateach.com