簡介

ARM9TDMI

ARM9TDMI ARM9TDMI是基於ARM體系結構v4版本的高端ARM核(注意:核並非晶片,ARM核與其他部件(如RAM、ROM、片內外設)組合在一起才構成現實的晶片)。ARM9TDMI是從ARM7核發展而來的。ARM9TDMI後綴的涵義如下:

T:支持高密度Thumb指令集擴展;

D:支持片上調試;

M:支持64位乘法指令;

I:帶EmbeddedICE硬體仿真功能模組。

ARM9TDMI-S是ARM9TDMI的可綜合(synthesizable)版本(軟核),對套用工程師來說,除非晶片生產廠商對ARM9TDMI-S進行了裁剪,否則在邏輯上ARM9TDMI-S與ARM9IDMI沒有太大區別,其編程模型與ARM7TDMI一致。

ARM9與ARM7TDMI比較

ARM

ARMARM9TDMI和ARM7TDMI分別是ARM9和ARM7系列晶片的處理器核,下面將從與ARM7TDMI做比較的角度闡述ARM9TDMI的特點。

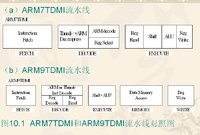

ARM9系列處理器和ARM7系列處理器的最大區別就是指令執行過程由原來的3級流水線(取指、解碼和執行),變成了5級流水線(取址、解碼、執行、數據存儲器/數據cache訪問和暫存器回寫)。兩種核心的指令執行流水線對照圖如圖10.1所示。其中ARM9TDMI的第四步,數據存儲器訪問操作主要作用是更新數據cache中的數據,實際上是對數據cache的訪問。

ARM7TDMI和ARM9TDMI流水線對照圖

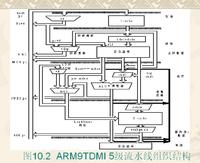

ARM9TDMI5級流水線組織結構圖如圖10.2所示。

ARM9TDMI和ARM7TDMI相比,其中的解碼部分是通過硬體實現Thumb指令解碼,即執行Thumb指令時由ARM7TDMI的軟解碼到ARM9TDMI的Thumb指令的硬解碼,這使得ARM9TDMI相對ARM7TDMI的解碼速度提高了。

ARM9TDMI同ARM7TDMI相比較除了採用硬體Thumb解碼外,其指令流水線由3級變成5級也使得程式的執行時間縮短了,這是根據程式的執行時間Tprog,由式(10.1)決定。

ARM9TDMI和ARM7TDMI相比,其中的解碼部分是通過硬體實現Thumb指令解碼,即執行Thumb指令時由ARM7TDMI的軟解碼到ARM9TDMI的Thumb指令的硬解碼,這使得ARM9TDMI相對ARM7TDMI的解碼速度提高了。

ARM9TDMI同ARM7TDMI相比較除了採用硬體Thumb解碼外,其指令流水線由3級變成5級也使得程式的執行時間縮短了,這是根據程式的執行時間Tprog,由式(10.1)決定。

ARM

ARM10.1式(10.1)中,Ninst:即程式中執行的ARM指令數;CPI:即平均每條指令的時鐘周期數;FCLK:表示處理器時鐘頻率。這樣對於給定的程式即Ninst固定的情況下,只有通過提高處理器時鐘頻率fclk和增加平均每條指令時鐘周期數CPI的方法來縮短程式執行的時間,提高處理器的執行能力。這樣如果同一指令的執行時間在處理器的時鐘頻率不方便更改時,可以通過更改CPI以顯著地縮短程式執行時間。

雖然ARM7TDMI和ARM9TDMI都是基於ARM體系結構的v4T版本,但在數據中止模式時ARM9TDMI採用的是基地址重新裝入(baserestoreddataabortmodel)模式,而ARM7TDMI採用的是基址更新模式(baseupdateddataabortmodel)。在ARM9TDMI中,當出現訪問存儲器數據中止時,處理器硬體在數據中止指令執行前,自動保存相應發生數據中止時基地址暫存器的值,這樣消除了數據中止句柄去一一查找引起數據中止操作的指令確定的基地址暫存器更新。

ARM7TDMI是基於馮·諾依曼體系結構,而ARM9TDMI是基於哈佛結構。一般將這兩個結構放在一起進行對比說明時,主要是指存儲器結構設計不同。在早期設計中馮·諾依曼體系結構將指令存儲器和數據存儲器放在一起,而後期的哈佛結構是將兩者分開的。

後者在處理器的設計中增加了cache,把指令cache和數據cache分開實現並且相應的MMU也分開實現,就形成了現在的哈佛結構。而把指令和數據cache放在一起是馮·諾依曼體系結構的特點。下面簡單分析這兩種體系的優缺點。

馮·諾依曼結構是在同一個存儲空間取指令和數據,兩者分時復用一條匯流排,故限制了工作頻寬,使控制電路較複雜。哈佛結構,指令和數據空間完全分開,可以同時訪問,且一次讀出從而減少存貯器的讀取次數,簡化控制電路,方便實現流水線。

在馮·諾依曼體系結構中,數據和程式存儲器是共享數據匯流排。數據匯流排共享有很多優點,比如減小匯流排開銷、能夠把RAM映射到程式空間。而對於哈佛體系結構的計算機,程式和數據匯流排是分開的,即程式存儲器和數據存儲器是兩個相互獨立的存儲器,每個存儲器獨立編址、獨立訪問。程式存儲器和數據存儲器獨立編址的優勢在於能夠在一個時鐘周期內同時讀取程式和數據,這樣就相應地減少了執行每一條指令所需的時鐘周期,即可以達到高速、並行工作。

還有一點就是ARM9TDMI可以完全執行ARM體系結構v4和v4T的未定義異常指令擴展空間上的指令集,而ARM7TDMI是不能執行的。這些指令擴展空間包括:算術指令擴展空間、控制指令擴展空間、協處理器指令擴展空間和載入/存儲擴展空間。

存儲器的字與半字

ARM處理器使用了馮·諾依曼(vonNeumann)結構,提供單一的主存接口。比如ARM7處理器就是標準的馮·諾依曼(vonNeumann)結構。而ARM9處理器的CPU/MMU/CACHE系統是指令和數據分開的,不過通常也還是提供單一的主存接口,因此ARM9處理器也可以看成是哈佛(Harvard)結構。從大的方面講,無論哪種ARM處理器結構,都可以看成是是馮·諾依曼(vonNeumann)結構,指令和數據共用一條32位匯流排,因此只有裝載、存儲和交換指令可以對存儲器中的數據進行訪問。

ARM處理器直接支持8位位元組、16位半字或者32位字的數據類型。其中,以能被4整除的地址開始連續的4個位元組構成1個字,字的數據類型為4個連續的位元組。從偶數地址開始連續的2個位元組構成一個半字,半字的數據類型為2個連續的位元組。ARM指令的長度剛好是1個字,Thumb指令的長度剛好是一個半字。

如果一個數據是以字方式存儲的,那么它就是字對齊的,否則就是非字對齊的。如果一個數據是以半字方式存的,那么它就是半字對齊的,否則就是非半字對齊的,半字與字對齊的實際情況見表2.1。

ARM技術服務企業:

矽谷芯微技術中心,它是一家電子行業的知名企業,該企業主要面向全社會進行ARM技術服務。