基本內容

簡併半導體:當雜質濃度超過一定數量後,載流子開始簡併化的現象稱為重摻雜(施主雜質或是受主雜質的濃度很大),即費米能級進入了價帶或導帶的半導體。

1、 簡併半導體中雜質不能充分電離:通過分析計算,室溫下,n型矽摻磷,發生簡併的磷雜質濃度 ,經計算,電離施主濃度 ,因此矽中只有8.4%的雜質是電離的,但摻雜濃度較大,所以電子濃度還是較大。簡併半導體中雜質不能充分電離的原因:簡併半導體電子濃度較高,費米能級較低摻雜時,遠在施主能級之上,使雜質電離程度降低(參閱§3.4 雜質能級上的電子和空穴)

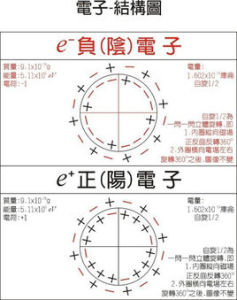

電子-內部結構模型圖

電子-內部結構模型圖2、 雜質帶導電:在非簡併半導體中,雜質濃度不算很大,雜質原子間距離比較遠,它們間的相互作用可以忽略。被雜質原子束縛的電子在原子之間沒有共有化運動,因此在禁帶中形成孤立的雜質能級。但是在重摻雜的簡併半導體中,雜質濃度很高,雜質原子互相間很靠近,被雜質原子束縛的電子的波函式顯著重疊,雜質電子就有可能在雜質原子之間產生共有化運動,從而使孤立的雜質能級擴展為能帶,通常稱為雜質能帶。雜質能帶中的雜質電子,可以通過雜質原子之間的共有化運動參加導電的現象稱為雜質帶導電。

3、 簡併化條件:簡併化條件是人們的一個約定,把 與 的相對位置作為區分簡併化與非簡併化的標準,一般約定:

Ec-Ef<=0 簡併

0< Ec-Ef<=2KT 弱簡併

Ec-Ef>2KT 非簡併

注意:

半導體發生簡併對應一個溫度範圍:用圖解的方法可以求出半導體發生簡併時,對應一個溫度範圍。這個溫度範圍的大小與發生簡併時的雜質濃度及雜質電離能有關:電離能一定時,雜質濃度越大,發生簡併的溫度範圍越大;發生簡併的雜質濃度一定時,雜質電離能越小,簡併溫度範圍越大。

1、 簡併半導體的載流子濃度:對於n型半導體,施主濃度很高,使費米能級接近或進入導帶時,導帶底附近底量子態基本上已被電子占據,導帶中底電子數目很多的條件不能成立,必須考慮泡利不相容原理的作用。這時,不能再用玻耳茲曼分布函式,必須用費米分布函式來分析導帶中電子的分布問題。這種情況稱為載流子的簡併化。發生載流子簡併化的半導體稱為基本半導體,對於p型半導體,其費米能級接近價帶頂或進入價帶,也必須用費米分布函式來分析價帶中空穴的分布問題。

2、 簡併時的雜質濃度:對n型半導體,半導體發生簡併時,摻雜濃度接近或大於導帶底有效狀態密度;對於雜質電離能小的雜質,則雜質濃度較小時就會發生簡併。對於p型半導體,發生簡併的受主濃度接近或大於價帶頂有效狀態密度,如果受主電離能較小,受主濃度較小時就會發生簡併。

對於不同種類的半導體,因導帶底有效狀態密度和價帶頂有效密度各不相同。一般規律是有效狀態密度小的材料,其發生簡併的雜質濃度較小。

3.一般價錢比較貴。