簡介

在數字電路通常分為組合邏輯電路和時序邏輯電路兩大類,組合邏輯電路的有關內容在前面的章節里已經作了介紹,組合邏輯電路的特點是輸入的變化直接反映了輸出的變化,其輸出的狀態僅取決於輸入的當前的狀態,與輸入、輸出的原始狀態無關,而時序電路是一種輸出不僅與當前的輸入有關,而且與其輸出狀態的原始狀態有關,

時序邏輯電路

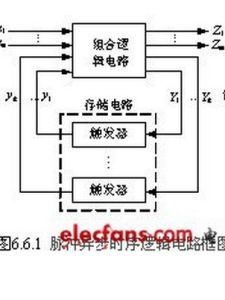

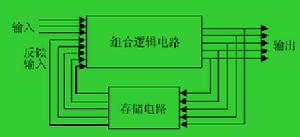

時序邏輯電路 從上面的圖上可以看出,其輸出是輸入及輸出前一個時刻的狀態的函式,這時就無法用組合邏輯電路的函式表達式的方法來表示其輸出函式表達式了,在這裡引入了現態(Present state)和次態(Next State)的概念,當現態表示現在的狀態(通常用Qn來表示),而次態表示輸入發生變化後其輸出的狀態 (通常用Qn 1表示),那么輸入變化後的輸出狀態表示為

Qn 1=f(X,Qn)

其中:X為輸入變數。

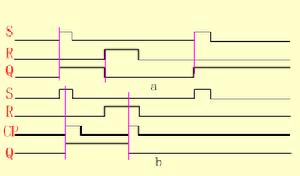

下面通過兩個波形圖來幫助建立時序電路中存儲器的概念:

時序邏輯電路

時序邏輯電路 從上圖a圖中可以看出,其圖中有四段輸入RS都為0的情況,但其輸出Q的狀態不同,這取決於輸出的原始狀態;而b圖中的輸入與圖a相同,但多了一個CP,這時輸出Q不僅取決於輸入RS、輸出Q的原始狀態,而且取決CP的狀態,僅當CP為高電平時,輸入的狀態才能影響輸出的狀態。通常將上面的兩種類型分為兩種形式的存儲器電路:鎖存器(Latch)和觸發器(Flip-flop),其兩都的區別在於其輸出狀態的變化是否取決於CP(時鐘脈衝Clock Plus)。將圖a所有的電路稱為鎖存器,而b圖所示的電路稱為觸發器電路。

時序邏輯電路的特點:任意時刻的輸出不僅取決於該時刻的輸入,而且還和電路原來的狀態有關,所以時序電路具有記憶功能。

特點

時序邏輯電路其任一時刻的輸出不僅取決於該時刻的輸入,而且還與過去各時刻的輸入有關。常見的時序邏輯電路有觸發器、計數器、暫存器等。由於時序邏輯電路具有存儲或記憶的功能,檢修起來就比較複雜。

帶有時序邏輯電路的數字電路主要故障分析:

1. 時鐘:時鐘是整個系統的同步信號,當時鐘出現故障時會帶來整體的功能故障。時鐘脈衝丟失會導致系統數據匯流排、地址匯流排或控制匯流排沒有動作。時鐘脈衝的速率、振幅、寬度、形狀及相位發生變化均可能引發故障。

2. 復位:含有微處理器(MPU)的設備,即使是最小系統,一般都具有復位功能。復位脈衝在系統上電時載入到MPU上,或在特定情況下使程式回到最初狀態(例如,看門狗Watchdog程式)。當復位脈衝不能發生、信號過窄、信號幅度不對、轉換中有干擾或轉換太慢時,程式就可能在錯誤的地址啟動,導致程式混亂。

3. 匯流排:匯流排傳遞指令系列和控制事件,一般有地址匯流排、數據匯流排和控制匯流排。當匯流排即使只有一位發生錯誤時,也會嚴重影響系統功能,出現錯誤定址、錯誤數據或錯誤操作等。匯流排錯誤可能發生在匯流排驅動器中,也可能發生在接收數據位的其它元件中。

4. 中斷:帶微處理器(MPU)的系統一般都能夠回響中斷信號或設備請求,產生控制邏輯,以暫時中斷程式執行,轉到特殊程式,為中斷設備服務,然後自動回到主程式。中斷錯誤主要是中斷線路粘附或受到干擾。

5. 信號衰減和畸變:長的並行匯流排和控制線可能會發生互動串擾和傳輸線故障,表現為相鄰的信號線出現尖峰脈衝(互動串擾),或驅動線上形成減幅振盪(相當於邏輯電平的多次轉換),從而可能加入錯誤數據或控制信號。發生信號衰減的可能原因比較多,常見的有高濕度環境、長的傳輸線、高速率轉換等。而大的電子干擾源會產生電磁干擾,導致信號畸變,引起電路的功能紊亂。

檢修方法

在檢修時序邏輯電路之前應儘可能熟悉系統的結構原理和電路,然後是分析故障的表征特性,儘可能地縮小故障產生的範圍。較高檔的醫療設備一般帶有自診斷程式,可充分利用它查找故障,將故障定位到較小範圍。

檢查電源

時序邏輯電路較常採用±5V、±15V、±12V 電源。當電源對地短路或電源穩定性差都可能導致系統故障,表現為系統無反應、系統程式紊亂等。一般來說,電源對地短路是因為 電容(去耦電容)短路產生的,找到故障電容最好的辦法是採用電流跟蹤儀跟蹤短路電流,沒有電流跟蹤儀的就只好將電路分單元查找替換。檢查時鐘

時鐘電路一般由石英晶體電路組成(也有採用 RC振盪電路的)。根據經驗, 石英晶體較易損壞。可用示波器測試時鐘信號的頻率、振幅、相位,或簡單地用邏輯探針檢測時鐘脈衝的有無。對各個單元電路的時鐘均應檢測,以防斷線、鬆脫、干擾等引起時鐘脈衝的不正確。檢查匯流排

用邏輯探針檢查匯流排上是否有脈衝活動。若匯流排上沒有脈衝活動,可繼續檢查匯流排驅動器輸入端有無脈衝信號、驅動器是否在允許狀態、驅動器是否回響激勵等,來確定故障是否是由於匯流排 驅動器引起的,然後輪流檢查每一個匯流排接收者。另外,可以關掉電源,用多用表檢查匯流排各線的對地電阻,如果所有線的阻值一樣,那么匯流排估計正常;如果一條或多條線的阻值與其餘的不同,那么該線值得懷疑;如果有兩根線的阻值相同,而又高於或低於其它的線,那么這兩條線可能相互短路了。檢查關鍵的脈衝信號

用邏輯探針、示波器或邏輯分析儀觀察復位、使能、選通、讀寫、中斷、讀記憶體等控制信號,可以較好地判斷 積體電路(IC)是否正常工作。當復位信號有效時,IC輸出應被清零或置位,程式應回到初始狀態運行;當使能信號有效而時鐘脈衝正常時,IC數據線上應有脈衝活動;當邏輯探針連到讀記憶體線上,而指示燈沒有閃爍顯示(即讀記憶體線上沒有脈衝活動),說明微處理器可能在程式的某處卡住了,因為每一條指令讀地址處存儲器時,讀記憶體線上通常是應有脈衝信號的;對於中斷信號,可用邏輯探針來觀察是否發生中斷線路粘附,也可通過外加直流電壓或低電平來控制(允許或禁止)被測試的中斷。檢查接口

接口卡、印刷板與 插座插接時可能鬆脫或偏離中心導致接觸不良而引發故障,實際上很多故障的確是由此產生的,對此可用無水酒精擦拭清潔接口後再重新插接固定。另外數字系統還常常通過外部通信線路(RS232、MODEM、IEEE-488等)與其它系統連線,而連線線通常很長,還可能暴露於電子干擾源下,例如繼電器、電機、變壓器、大型X線機、陰雨天閃電等,連線口接觸不良和電子干擾源的電磁干擾(EMI)均可能會產生錯誤的數據傳送,甚至損壞相關的元件。對 電磁干擾最好找出干擾源後排除它,其次可改善工作環境(如濕度和溫度等),加強禁止,或改用禁止性能好的連線線。時序邏輯電路的檢修有許多方法技巧,必須通過長期實際工作摸索總結經驗,才能更好地診斷、發現、排除故障,提高時序邏輯電路的維修技術水平。