技術簡介

快取的工作原理是當CPU要讀取一個數據時,首先從快取中查找,如果找到就立即讀取並送給CPU處理;如果沒有找到,就用相對慢的速度從記憶體中 讀取並送給CPU處理,同時把這個數據所在的數據塊調入快取中,可以使得以後對整塊數據的讀取都從快取中進行,不必再調用記憶體。

正是這樣的讀取機制使CPU讀取快取的命中率非常高(大多數CPU可達90%左右),也就是說CPU下一次要讀取的數據90%都在快取中,只有 大約10%需要從記憶體讀取。這大大節省了CPU直接讀取記憶體的時間,也使CPU讀取數據時基本無需等待。總的來說,CPU讀取數據的順序是先快取後記憶體。

最早先的CPU快取是個整體的,而且容量很低,英特爾公司從Pentium時代開始把快取進行了分類。當時集成在CPU核心中的快取已不足以滿 足CPU的需求,而製造工藝上的限制又不能大幅度提高快取的容量。因此出現了集成在與CPU同一塊電路板上或主機板上的快取,此時就把 CPU核心集成的緩 存稱為一級快取,而外部的稱為二級快取。一級快取中還分數據快取(I-Cache)和指令快取(D-Cache)。二者分別用來存放數據和執行這些數據的 指令,而且兩者可以同時被CPU訪問,減少了爭用Cache所造成的衝突,提高了處理器效能。英特爾公司在推出Pentium 4處理器時,還新增了一種一級追蹤快取,容量為12KB.

隨著CPU製造工藝的發展,二級快取也能輕易的集成在CPU核心中,容量也在逐年提升。再用集成在CPU內部與否來定義一、二級快取,已不 確切。而且隨著二級快取被集成入CPU核心中,以往二級快取與CPU大差距分頻的情況也被改變,此時其以相同於主頻的速度工作,可以為CPU提供更高的傳 輸速度。

二級快取是cpu性能表現的關鍵之一,在CPU核心不變化的情況下,增加二級快取容量能使性能大幅度提高。而同一核心的CPU高低端之分往往也是在二級快取上有差異,由此可見二級快取對於CPU的重要性。

CPU在快取中找到有用的數據被稱為命中,當快取中沒有CPU所需的數據時(這時稱為未命中),CPU才訪問記憶體。從理論上講,在一顆擁有二級 快取的CPU中,讀取一級快取的命中率為80%。也就是說CPU一級快取中找到的有用數據占數據總量的80%,剩下的20%從二級快取中讀取。由於不能準 確預測將要執行的數據,讀取二級快取的命中率也在80%左右(從二級快取讀到有用的數據占總數據的16%)。那么還有的數據就不得不從記憶體調用,但這已經 是一個相當小的比例了。

較高端的CPU中,還會帶有三級快取,它是為讀取二級快取後未命中的數據設計的—種快取,在擁有三級快取的CPU中,只有約 5%的數據需要從記憶體中調用,這進一步提高了CPU的效率。

Intel二級快取

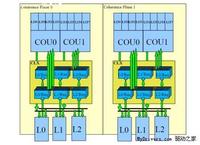

Intel的雙核心CPU主要有Pentium D、Pentium EE、Core Duo三種,其中Pentium D、Pentium EE的二級快取方式完全相同。Pentium D和Pentium EE的二級快取都是CPU內部兩個核心具有互相獨立的二級快取,其中,8xx系列的Smithfield核心CPU為每核心1MB,而9xx系列的 Presler核心CPU為每核心2MB。這種CPU內部的兩個核心之間的快取數據同步是依靠位於主機板北橋晶片上的仲裁單元通過前端匯流排在兩個核心之間傳 輸來實現的,所以其數據延遲問題比較嚴重,性能並不盡如人意。

Core Duo使用的核心為Yonah,它的二級快取則是兩個核心共享2MB的二級快取,共享式的二級快取配合Intel的“Smart cache”共享快取技術,實現了真正意義上的快取數據同步,大幅度降低了數據延遲,減少了對前端匯流排的占用,性能表現不錯,是雙核心處理器上最先進的二級快取架構。今後Intel的雙核心處理器的二級快取都會採用這種兩個核心共享二級快取的“Smart cache”共享快取技術。

AMD雙二級快取

Athlon 64 X2 CPU的核心主要有Manchester和Toledo兩種,他們的二級快取都是CPU內部兩個核心具有互相獨立的二級快取,其中,Manchester 核心為每核心512KB,而Toledo核心為每核心1MB。處理器內部的兩個核心之間的快取數據同步是依靠CPU內置的System Request Interface(系統請求接口,SRI)控制,傳輸在CPU內部即可實現。這樣一來,不但CPU資源占用很小,而且不必占用記憶體匯流排資源,數據延遲也 比Intel的Smithfield核心和Presler核心大為減少,協作效率明顯勝過這兩種核心。不過,由於這種方式仍然是兩個核心的快取相互獨立, 從架構上來看也明顯不如以Yonah核心為代表的Intel的共享快取技術Smart Cache。

二級快取事項

快取是數據由記憶體通往CPU的橋樑。它的速度比記憶體快得多,但是容量也比記憶體小的多。同時快取依據讀取速度和容量進一步分為一級和二級。在CPU需要數據的時候,遵循一級快取—〉二級快取—〉記憶體的順序,從而儘量提高讀取速度。這樣“快取+記憶體”的系統就同時兼具了速度和容量的優點。二級快取容量對性能的影響是漸漸減弱的,當二級快取從沒有增長到128KB時,帶來的性能提升可能是直線上升的。但是當它從2MB增長到4MB的時候,可能使用者甚至感覺不到性能的提升。這是因為在當前CPU所處理數據的過程中,幾乎無時不刻需要用到128KB以下的快取,但是需要用到1MB以上快取的時候很少(2%左右)。因此雖然二級快取越漲越大,實際上對CPU性能的影響卻是越來越小的。因此,完全不必要盲目追求二級快取的高容量,夠用就好。

指令快取和指令追蹤快取

快取存儲的內容不止是數據,也包括指令,但是由於指令具備的以下性質,導致指令快取的機制遠沒有數據快取那么複雜:

需要執行的代碼量通常都是比較固定的,和問題的複雜度有關 程式指令通常由編譯器產生,產生過程中就能得到一定的最佳化 相比數據存取機制,程式流程的可預測度要強得多,更有利於prefeching 代碼一般都具有很好的空間和時間局部性

隨著技術的發展,CPU的執行過程都流水化了,指令的執行都是分成階段的,一開始安心等在指令快取中,等待被處理單元執行時才取出,然後解碼,準備相關參數,最後執行。這種過程有兩個缺點,首先某些 x86 指令非常複雜,經由解碼器時需耗費太多的時間來解碼,尤其是以X86為代表的CISA家族,最糟的情況下所有解碼單元忙於解碼複雜指令,以至於阻礙處理器的執行管道。另一個問題則是如果在小循環的代碼中,每當這些代碼進入執行路徑幾次,編碼就得進行幾次,造成時間的浪費。而且大家知道的流水管線是越做越長,這也就意味著,一旦流水線遭遇不測發生中斷,或者出現分枝預測的錯誤,造成的延時就會很大。可以說,這算是一個一直困擾CPU設計人員的問題。

從Pentium 4開始,Intel採用了一種新的快取類型,叫trace cache,俗稱指令追蹤快取。這玩意不是用來和一般的指令快取一樣存儲指令的原始位元組序列,而是被用來存儲解碼單元送出來的微操作。

指令追蹤快取位於指令解碼器和核心第一層計算管線之間,指令在解碼單元內獲取和解碼之後,微操作必須先經過追蹤快取的存儲和和輸出,才能到達核心第一層計算管線被執行。這樣可以有效彌補上述兩個缺點,因為此時所取的都是解碼後的指令,還避免了指令的重複調用。更重要的是,追蹤快取確保處理器管道持續處於指令滿載的狀態,避免執行路徑由於解碼單元延遲的情況。應該說,指令追蹤快取確實是一個值得稱道的技術。

當然,這些分析都是基於L1I快取分析的,至於L2的快取,因為是數據和指令統一存儲,自然就不可能作出和追蹤快取類似的架構了。

CPU的L1指令快取和L1高速快取的關係

L1高速快取,也就是我們經常說的一級高速快取。在CPU裡面內置了高速快取可以提高CPU的運行效率。內置的L1高速快取的容量和結構對CPU的性能影響較大,不過高速緩衝存儲器均由靜態RAM組成,結構較複雜,在CPU管芯面積不能太大的情況下,L1級高速快取的容量不可能做得太大。採用回寫(Write Back)結構的高速快取。它對讀和寫*作均有可提供快取。而採用寫通(Write-through)結構的高速快取,僅對讀*作有效。在486以上的計算機中基本採用了回寫式高速快取。在目前流行的處理器中,奔騰Ⅲ和Celeron處理器擁有32KB的L1高速快取,奔騰4為8KB,而AMD的Duron和Athlon處理器的L1高速快取高達128KB。

L2高速快取,指CPU第二層的高速快取,第一個採用L2高速快取的是奔騰 Pro處理器,它的L2高速快取和CPU運行在相同頻率下的,但成本昂貴,市場生命很短,所以其後奔騰 II的L2高速快取運行在相當於CPU頻率一半下的。接下來的Celeron處理器又使用了和CPU同速運行的L2高速快取,現在流行的CPU,無論是AthlonXP和奔騰4,其L2高速快取都是和CPU同速運行的。除了速度以外,L2高速快取容量也會影響CPU的性能,原則是越大越好,現在家庭用CPU容量最大的是512KB,而伺服器和工作站上用CPU的L2高速快取更高達1MB-3MB。

cpuL1快取首先是CPU的內部結構決定,CPU是由矽晶原片切割而成的,一塊晶原片切割的CPU塊有限,所以一個CPU的結構要非常合理地搭配L1,L2快取大小,P4640比P4630高頻,所以內部結構有所不同。而L1快取的作用是數據交換的“超高速”通道,所以其大小不是重點,內部參數才是關鍵,只要參數(CL值,延遲等)夠快,完全可以彌補大小的差距,像P-M 1。7G的CPU由於L1快取的參數夠高,雖然容量有不足,但在性能測試上L1快取的速度比P4 630快的多。所以不必刻意要求L1快取大小。(另外,CPU的快取速度比一般記憶體快的多,大概快幾十倍)

高速快取英文是cache。一種特殊的存儲器子系統,其中複製了頻繁使用的數據,以利於CPU快速訪問。存儲器的高速緩衝存儲器存儲了頻繁訪問的 RAM 位置的內容及這些數據項的存儲地址。當處理器引用存儲器中的某地址時,高速緩衝存儲器便檢查是否存有該地址。如果存有該地址,則將數據返回處理器;如果沒有保存該地址,則進行常規的存儲器訪問。因為高速緩衝存儲器總是比主RAM 存儲器速度快,所以當 RAM 的訪問速度低於微處理器的速度時,常使用高速緩衝存儲器。

技術套用

為了提高高速DSP或通用處理器的程式執行速度,描述了一種指令快取單元的有效架構,特別是實現細節和性能分析.因所提出的指令快取單元是為一種高性能VLIW結構的DSP核而設計,使用了並行的標籤比較邏輯和暫存器堆的結構,晶片面積、關鍵路徑延遲、功耗都大大減小.該指令快取單元使用高層次的RTL(使用Verilog)編碼,並由Synopsys的Design Compiler綜合,使用不同的StarCoreTM基準程式測試比較,並進行性能分析.比較結果表明,所提出的結構是有效的,適合用於任何高速的處理器。

一級指令快取

CPU快取(Cache Memory)是位於CPU與記憶體之間的臨時存儲器,它的容量比記憶體小的多但是交換速度卻比記憶體要快得多。快取的出現主要是為了解決CPU運算速度與記憶體讀寫速度不匹配的矛盾,因為CPU運算速度要比記憶體讀寫速度快很多,這樣會使CPU花費很長時間等待數據到來或把數據寫入記憶體。在快取中的數據是記憶體中的一小部分,但這一小部分是短時間內CPU即將訪問的,當CPU調用大量數據時,就可避開記憶體直接從快取中調用,從而加快讀取速度。由此可見,在CPU中加入快取是一種高效的解決方案,這樣整個記憶體儲器(快取+記憶體)就變成了既有快取的高速度,又有記憶體的大容量的存儲系統了。快取對CPU的性能影響很大,主要是因為CPU的數據交換順序和CPU與快取間的頻寬引起的。

快取的工作原理是當CPU要讀取一個數據時,首先從快取中查找,如果找到就立即讀取並送給CPU處理;如果沒有找到,就用相對慢的速度從記憶體中讀取並送給CPU處理,同時把這個數據所在的數據塊調入快取中,可以使得以後對整塊數據的讀取都從快取中進行,不必再調用記憶體。

正是這樣的讀取機制使CPU讀取快取的命中率非常高(大多數CPU可達90%左右),也就是說CPU下一次要讀取的數據90%都在快取中,只有大約10%需要從記憶體讀取。這大大節省了CPU直接讀取記憶體的時間,也使CPU讀取數據時基本無需等待。總的來說,CPU讀取數據的順序是先快取後記憶體。

目前快取基本上都是採用SRAM存儲器,SRAM是英文Static RAM的縮寫,它是一種具有靜志存取功能的存儲器,不需要刷新電路即能保存它內部存儲的數據。不像DRAM記憶體那樣需要刷新電路,每隔一段時間,固定要對DRAM刷新充電一次,否則內部的數據即會消失,因此SRAM具有較高的性能,但是SRAM也有它的缺點,即它的集成度較低,相同容量的DRAM記憶體可以設計為較小的體積,但是SRAM卻需要很大的體積,這也是目前不能將快取容量做得太大的重要原因。它的特點歸納如下:優點是節能、速度快、不必配合記憶體刷新電路、可提高整體的工作效率,缺點是集成度低、相同的容量體積較大、而且價格較高,只能少量用於關鍵性系統以提高效率。

按照數據讀取順序和與CPU結合的緊密程度,CPU快取可以分為一級快取,二級快取,部分高端CPU還具有三級快取,每一級快取中所儲存的全部數據都是下一級快取的一部分,這三種快取的技術難度和製造成本是相對遞減的,所以其容量也是相對遞增的。當CPU要讀取一個數據時,首先從一級快取中查找,如果沒有找到再從二級快取中查找,如果還是沒有就從三級快取或記憶體中查找。一般來說,每級快取的命中率大概都在80%左右,也就是說全部數據量的80%都可以在一級快取中找到,只剩下20%的總數據量才需要從二級快取、三級快取或記憶體中讀取,由此可見一級快取是整個CPU快取架構中最為重要的部分。

一級快取(Level 1 Cache)簡稱L1 Cache,位於CPU核心的旁邊,是與CPU結合最為緊密的CPU快取,也是歷史上最早出現的CPU快取。由於一級快取的技術難度和製造成本最高,提高容量所帶來的技術難度增加和成本增加非常大,所帶來的性能提升卻不明顯,性價比很低,而且現有的一級快取的命中率已經很高,所以一級快取是所有快取中容量最小的,比二級快取要小得多。

一般來說,一級快取可以分為一級數據快取(Data Cache,D-Cache)和一級指令快取(Instruction Cache,I-Cache)。二者分別用來存放數據以及對執行這些數據的指令進行即時解碼,而且兩者可以同時被CPU訪問,減少了爭用Cache所造成的衝突,提高了處理器效能。目前大多數CPU的一級數據快取和一級指令快取具有相同的容量,例如AMD的Athlon XP就具有64KB的一級數據快取和64KB的一級指令快取,其一級快取就以64KB+64KB來表示,其餘的CPU的一級快取表示方法以此類推。

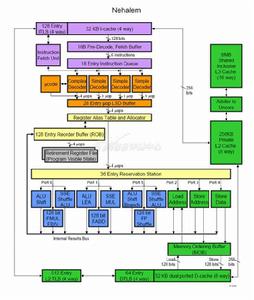

Intel的採用NetBurst架構的CPU(最典型的就是Pentium 4)的一級快取有點特殊,使用了新增加的一種一級追蹤快取(Execution Trace Cache,T-Cache或ETC)來替代一級指令快取,容量為12KμOps,表示能存儲12K條即12000條解碼後的微指令。一級追蹤快取與一級指令快取的運行機制是不相同的,一級指令快取只是對指令作即時的解碼而並不會儲存這些指令,而一級追蹤快取同樣會將一些指令作解碼,這些指令稱為微指令(micro-ops),而這些微指令能儲存在一級追蹤快取之內,無需每一次都作出解碼的程式,因此一級追蹤快取能有效地增加在高工作頻率下對指令的解碼能力,而μOps就是micro-ops,也就是微型操作的意思。它以很高的速度將μops提供給處理器核心。Intel NetBurst微型架構使用執行跟蹤快取,將解碼器從執行循環中分離出來。這個跟蹤快取以很高的頻寬將uops提供給核心,從本質上適於充分利用軟體中的指令級並行機制。Intel並沒有公布一級追蹤快取的實際容量,只知道一級追蹤快取能儲存12000條微指令(micro-ops)。所以,我們不能簡單地用微指令的數目來比較指令快取的大小。實際上,單核心的NetBurst架構CPU使用8Kμops的快取已經基本上夠用了,多出的4kμops可以大大提高快取命中率。而如果要使用超執行緒技術的話,12KμOps就會有些不夠用,這就是為什麼有時候Intel處理器在使用超執行緒技術時會導致性能下降的重要原因。

三級指令快取

三級快取機構圖

三級快取機構圖運作原理

其運作原理在於使用較快速的儲存裝置保留一份從慢速儲存裝置中所讀取數據且進行拷貝,當有需要再從較慢的儲存體中讀寫數據時,CACHE能夠使得讀寫的動作先在快速的裝置上完成,如此會使系統的回響較為快速。

三級快取分類 Cache(三級快取),分為兩種,早期的是外置,以後的升級產品都是內置的。而它的實際作用即是,L3快取的套用可以進一步降低記憶體延遲,同時提升大數據量計算時處理器的性能。降低記憶體延遲和提升大數據量計算能力對遊戲都很有幫助。而在伺服器領域增加L3快取在性能方面仍然有顯著的提升。比方具有較大L3快取的配置利用物理記憶體會更有效,故它比較慢的磁碟I/O子系統可以處理更多的數據請求。具有較大L3快取的處理器提供更有效的檔案系統快取行為及較短訊息和處理器佇列長度。

其實最早的L3快取被套用在AMD發布的K6-III處理器上,當時的L3快取受限於製造工藝,並沒有被集成進晶片內部,而是集成在主機板上。在只能夠和系統匯流排頻率同步的L3快取同主記憶體其實差不了多少。後來使用L3快取的是英特爾為伺服器市場所推出的Itanium處理器。接著就是P4EE和至強MP。Intel還打算推出一款9MB L3快取的Itanium2處理器,和以後24MB L3快取的雙核心Itanium2處理器。

但基本上L3快取對處理器的性能提高顯得不是很重要,比方配備1MB L3快取的Xeon MP處理器卻仍然不是Opteron的對手,由此可見前端匯流排的增加,要比快取增加帶來更有效的性能提升

一級指令快取,一級數據快取和二級快取的區別一級快取(Level 1 Cache)簡稱L1 Cache,位於CPU核心的旁邊,是與CPU結合最為緊密的CPU快取,也是歷史上最早出現的CPU快取。由於一級快取的技術難度和製造成本最高,提高容量所帶來的技術難度增加和成本增加非常大,所帶來的性能提升卻不明顯,性價比很低,而且現有的一級快取的命中率已經很高,所以一級快取是所有快取中容量最小的,比二級快取要小得多。

一般來說,一級快取可以分為一級數據快取(Data Cache,D-Cache)和一級指令快取(Instruction Cache,I-Cache)。二者分別用來存放數據以及對執行這些數據的指令進行即時解碼,而且兩者可以同時被CPU訪問,減少了爭用Cache所造成的衝突,提高了處理器效能。目前大多數CPU的一級數據快取和一級指令快取具有相同的容量,例如AMD的Athlon XP就具有64KB的一級數據快取和64KB的一級指令快取,其一級快取就以64KB+64KB來表示,其餘的CPU的一級快取表示方法以此類推。

二級快取是CPU性能表現的關鍵之一,在CPU核心不變化的情況下,增加二級快取容量能使性能大幅度提高。而同一核心的CPU高低端之分往往也是在二級快取上有差異,由此可見二級快取對於CPU的重要性。