目前,CMOS工藝在積體電路特別是數字IC中套用得很普遍。由於CMOS電路在輸入穩定的時候總有一個管子截止,所以它的靜態功耗在理想情況下應該是零,但這並不代表靜態功耗真的為零,實際上CMOS電路的靜態功耗就是指電路中的漏電流(這裡不考慮亞閾值電流)。 CMOS電路功耗的主要來源是動態功耗,它由兩部分組成:開關電流和短路電流。所以,整個CMOS電路的功耗如右式所示。

CMOS電路功耗公式

CMOS電路功耗公式其中:

第一部分P是開關電流產生的動態功耗;

第三部分P是動態情況下P管和N管同時導通時的短路電流產生的動態功耗;

而第二部分P是由擴散區和襯底之間的反向偏置漏電流產生的靜態功耗。

在這三項中,第一部分P大約占電路功耗的80% ,因而這裡就只考慮開關電流所產生的動態功耗。

開關電流是這樣產生的:在CMOS電路,當輸入為“0”時,PMOS導通,電源通過 PMOS向負載電容充電;而當電路輸入為“1” 時,負載電容又會通過NMOS向地放電。開關電流就是不斷對負載電容充放電所產生的。

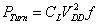

一個CMOS反相器由開關電流引起的平均動態功耗如下式所示。

pturn的公式

pturn的公式其中:CL是負載電容,VDD是電路的電壓,f是時鐘頻率。

Pleakage=Vdd*ileakage

其中:Vdd是電路的電壓,ileakage是漏電電流

Pshort=f*Vdd*ishort

其中:f是時鐘頻率,Vdd是電路的電壓,ishort是短路電流

所以,要想降低電路的功耗就應該降低電路的電壓和頻率。