超前/滯後控制

超前/滯後控制是指普遍採用前置計數器和後置計數器實現觸發點前後的採集樣點數的控制,提出用一個計數器實現觸發點前後的採集樣點數的控制的方案,例如:對於存儲深度深的數字示波器,可以大大減少資源,節約成本,對中價位數字示波器的生產和套用十分有利。

超前/滯後控制是數字示波器的時基電路中的核心,控制捕捉觸發點前後的信息。在數字示波器的設計中,無論是實時採樣示波器還是非實時採樣示波器(順序採樣、隨機採樣)多採用了超前/滯後控制的方案。設定觸發點前後的採集存儲樣點數,提供A/D採集轉化器後的數據緩衝器以及RAM的採集使能信號和採集結束信號,用來控制向RAM中啟動寫和停止寫採集數據,從而達到既能捕捉觸發點前的信號,又能捕捉觸發點後的信號。

電路核心

超前/滯後控制的核心是計數器。當前,國外(如HP公司)國內的數字示波器的超前/滯後控制採用了前置計數器和後置計數器的設計方案,前置計數器用於控制存儲器存儲捕捉觸發點前採集的採集樣點數,後置計數器用於控制存儲器存儲捕捉觸發後的採集樣點數。計數器的長度決定了示波器的存儲深度,前置計數器和後置計數器控制的總深度為存儲深度。存儲深度是示波器的性能的重要指標,存儲深度越大,對感興趣段的波形觀察就越方便。

為了減少資源,節約成本,減小體積,採用CPLD(或者FPGA)設計數字示波器中的時基電路。在2Gsps實時數字採樣示波器的研究項目基礎上,結合研製100MHz頻寬的隨機取樣數字存儲示波器(等效採樣率最大達到SGsps)的經驗,我們用一個計數器設計超前/滯後控制電路,實現超前/滯後採樣的控制。這對存儲深度很深的數字示波器,可以大大節約計數器占用了CPLD(或者FPGA)資源。

滯後一超前校正控制系統

滯後一超前校正控制系統的一種校正方式。是校正裝置的傳遞函式的一類串聯校正。

滯後一超前校正裝置的傳遞函式中,第一項產生超前校正的作用,第二項產生滯後校正的作用。當輸人為正弦信號時,此裝置的輸出是帶有相移的正弦信號,輸出信號的相移性質與輸人信號的頻率有關.當頻率低時,相移是滯後的;當頻率高時,相移是超前的。滯後一超前校正綜合了滯後校正和超前校正的優點,可同時改善系統的瞬態性能和穩態性能,即兼有快速回響特性和良好穩態精度。

超前/滯後電路的控制信號和邏輯時序

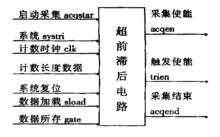

示波器的前置和後置計數器計數總深度設計為32K,前置計數器為15bit,後置計數器為15bit。兩個計數器的輸入控制信號有採集開始信號、系統觸發信號、計數時鐘、計數數據、系統復位和數據載入等信號。如圖1所示。

圖1超前/滯後電路輸入輸出信號

圖1超前/滯後電路輸入輸出信號在數據所存控制信號gate有效時數據裝入數據鎖存器中並鎖存。當採集啟動信號acqstar到來時,控制邏輯電路產生數據載入信號sload,將鎖存器的數據裝入超前/滯後電路中前後置計數器中,並產生採集使能信號,啟動前置計數器開始計數前置計數器計數滿後,關閉前置計數器,產生觸發使能信號,放開觸發電路產生的系統觸發信號systri,啟動後置計數器開始工作。當後置計數器計數滿數據時,產生採集結束信號,關閉採集使能信號。如圖2。

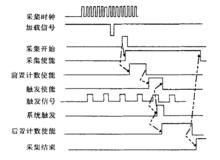

圖2超前/滯後電路信號時序示意圖

圖2超前/滯後電路信號時序示意圖超前/滯後計數功能設計和工作原理

根據前面所述的功能和時序,知道超前/滯後電路中前置計數器和後置計數器不是同時工作的,而是當前置計數器計數時,後置計數器不工作;當後置計數器計數時,前置計數器不工作,因此理論上就可以用一個計數器實現觸發點前後採樣點的計數。我們模擬圖2中的超前/滯後電路信號時序示意圖進行設計其相應的控制邏輯電路,見圖3所示。為了更好地理解電路的工作原理,下面結合信號具體進行闡述。

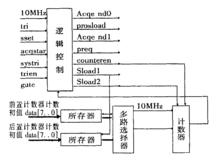

圖3用一個計數器實現超前/滯後控制電路原理圖

圖3用一個計數器實現超前/滯後控制電路原理圖鎖存器

電路中用兩個鎖存器(LATCH1, LATCH2)鎖存經CP U解讀來自示波器按鍵的控制信號後的數據,為計數器載入提供各種控制信號和數據。兩個鎖存器分別設計為16位,其中LATCH 1鎖存觸發點前的樣點數,並給前置計數器設定初始值,LATCH2鎖存觸發點後的樣點數,並給後置計數器設定初始值。鎖存器的數據所存控制信號gate控制鎖存,並為計數器置位。

計數器

用一個計數器實現觸發點前後的採集樣點數的計數,既用於設定採集觸發前的樣點數,又用於設定觸發信號到來後的採集樣點數。計數器的設計是本電路設計的重點和難點,我們將計數器設計為同步計數器,並帶有同步載入、異步置位、計數使能端,且均為高電平有效。由於其長度直接影響採集深度,我們根據廠方要求設計為32k。計數器的工作具體包括以下兩個環節:

A:當系統復位後,第一次接到啟動採集信號acqstar後,首先產生前置計數器載入信號,將LATCHI的初值裝入計數器,並且第一次啟動計數器工作。當計數器計滿後輸出前置計數器計數結束信號preq,且preq電平為“1",放開系統觸發信號systn。

B:當系統觸發信號到來時,產生後置計數器載入信號prosload信號,進而產生sload2信號,將LATCH2的鎖存值裝入計數器,並第二次啟動計數器工作。當計數器計滿後,電路中的2位計數器輸出acqend0和採集結束信號(acqendl), acqendl從0變為“1”時,表示觸發點後的採樣點已經采滿,關閉計數器的計數使能信號,停止計數器計數。

A環節和B環節的採集為一個完整的採集周期,A環節由採集啟動信號acqstar啟動;B環節在A環節結束後自動啟動。從仿真時序圖4可以看出:sloadl為A環節的同步載入信號,prosload為B環節的同步載入信號。當B環節完成後,電路進入等待狀態,等待採集啟動信號acqstart到來。當採集啟動信號acqstar到來後,電路又進入A環節工作狀態。這樣周而復始地循環。當 sloadl , sload2都為"1”時,計數器處於A環節,當sloadl為“0" , sload2為“1”時,計數器處於B環節。

以上兩個環節分別完成了設定的觸發點前和觸發點後的採集樣點數,A環節完成設定的觸發點前的採集樣點數;B環節完成設定的觸發點後的採集樣點數。

電路設計保證了計數器一旦啟動,且在計數期間(在完成設定的觸發點前和觸發點後的採集樣點數之內),採集啟動信號acqstar與否都不能影響計數器的工作。只有當計數器工作結束後(處於B環節),也就是當計數器完成了觸發點後的設定採集樣點數後,才能回響採集啟動信號acqstar這樣保證每次都能完成設定的採集存儲深度。我們可以從仿真時序圖中觀察設計的結果。

電路設計的另一個信號是計數器計數使能信號preen,這是一個難點和重點。

發展和改進

超前滯後控制策略中的實際微分環節、二階超前校正環節在實際的工程實踐中大量採用。然而,超前校正在改善系統動態性能的同時,其高通濾波特性也放大了高頻干擾!2],往往使超前校正難以發揮其預期效果,特別在有外部高頻干擾時容易造成調節機構的大幅波動,嚴重影響了調節機構與控制系統的品質要求,在實際工程實例中採用超前校正要非常小心謹慎。

為了克服超前策略存在的問題,在二階超前環節的基礎上,廣東電網公司電力科學研究院與珠海金灣電廠提出了一種改進型超前滯後控制策略,經過工程套用的實踐,證實了新型控制策略相對於常規的超前控制策略具有更好的優越性。

改良的二階超前校正環節

超前校正策略抵抗高頻干擾能力較差,根源在於該環節的高頻增益較大,對此,主要的改良方案為:在不改變相頻特性的前提下,對幅頻特性進行改造,降低高頻增益,使幅頻特性曲線在較寬的範圍內比較平滑。這樣,在較大幅度地改善系統動態性能指標的同時,又幾乎不增加調節器的高頻增益,在外部高頻干擾時不會造成調節機構的大幅波動,使系統具有較高的穩定性和可靠性。

二階超前校正環節改進實例

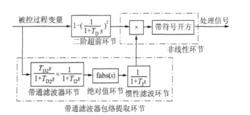

二階超前校正環節改進結構如圖1所示。

圖1二階超前校正環節改進示意圖

圖1二階超前校正環節改進示意圖圖1中,校正迴路主要由3個部分組成:二階超前校正環節;帶通濾波器包絡提取環節,該環節主要作用類似於包絡檢波電路;上述兩個環節輸出信號相乘然後開方構成的非線性環節,該環節起到信號重構並保證穩態時信號增益不變之作用。在兩個匹配網路中,對應的電路參數必須與整個控制迴路調製出的頻率相適應。

改進後二階超前環節頻率特性試驗

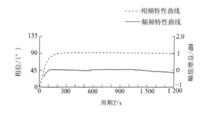

其頻率特性試驗結果如圖2所示。

圖2改良環節頻率特性圖

圖2改良環節頻率特性圖由圖2可以看出,在較寬的頻率範圍內,改進後環節的相位幾乎均為90°,而且其幅值增益近似為0dB。