測試分析

對於不同的CPU平台,記憶體頻寬的重要性不盡相同,而在與記憶體延時的搭配上,記憶體頻寬也有很多學問。好了,還是請大家看具體的測評。

1.AMD-nForce2平台的記憶體頻寬分析

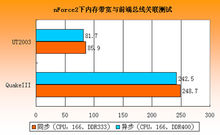

正是nForce2晶片組的出現才讓AthlonXP平台向更高的前端匯流排發展,而經過一段時間的超頻體驗,不少用戶都會前端匯流排與記憶體頻寬之間的關聯有了一定的認識。一般而言,我們的常理告訴我們記憶體頻率越高越好,因為它直接決定了記憶體頻寬。然而在nForce2晶片組中則並不是這樣一回事。由於記憶體控制器的特殊性,它要求DDR記憶體與CPU同步運行時才能達到最佳性能。下面是nForce2晶片組在記憶體同步/異步條件下的測試成績:

簡單說來,即CPU設定為166MHz外頻(333MHz前端匯流排)、DDR運行於DDR333模式時,其性能要比CPU設定為166MHz外頻、DDR運行於DDR400模式的方案更好。所以,無論在何種情況下,我們都建議nForce2用戶將“MemoryFrequency”設定為“Sync(同步)”。事實上,同樣的情況也出現在ALiMAGiK1和SiS745這兩款晶片組上,DDR333在不同步時性能反而不如DDR266同步,好在它們的市場份額並不大。

此外,當我們使用不集成顯示卡的SPP北橋時,單通道與雙通道之間的性能差距微乎其微,甚至都可以將微小的差距理解為測試誤差。而在使用集成顯示卡的IGP北橋中,雙通道確實展現出很大的優勢。毫無疑問,對於nForce2而言,雙通道儘管能夠提升記憶體頻寬,但是AthlonXP的前端匯流排利用不上,單通道DDR已經完全能夠滿足其需求。之所以nForce2能再KT400面前橫行霸道,其關鍵還在於記憶體控制器的效率,而非雙通道技術。

2.AMD-KT400A平台

VIA的KT400A也是一款主流SocketA晶片組,那么它究竟是否會出現高記憶體頻率異步時性能不佳的情況呢?請大家先不要忙著下結論,更應該拋棄以往對KT333/400的陳見,因為KT400A的記憶體控制器經過了VIA的重新設計。

顯然,KT400A已經能夠利用里DDR400的高頻寬,即便是在記憶體異步的情況下。現大家應該很明白在SocketA平台下的記憶體最佳化了吧,確實很簡單:nForce2要保持同步,而KT400A/600應該儘可能提高記憶體頻率。

3.Intel-I845PE平台

儘管單通道的I845PE晶片組已經略顯落伍,但是我們能夠從中分析出單通道情況下,記憶體頻寬的重要性。事實上,P4處理器很早就達到533MHz前端匯流排(133MHz外頻),此時只有使用DDR333才算是同步運行。

很明顯,DDR333的高記憶體頻寬在此表現出明顯的性能優勢,無論對3D遊戲還是商業套用軟體都大有裨益。事實上,單通道DDR對於Pentium4的Netburst架構而言僅僅是杯水車薪,即便是DDR333也無法滿足Pentium4的需求,因為533MHz前端匯流排的Pentium4必須擁有4。2GB/s的記憶體頻寬才能充分別發揮性能,而單通道的DDR333隻具備2。7GB/s,更不用說DDR266了。

4.Intel-I865PE

I865PE晶片組是如今毫無疑問的當紅小生,憑藉雙通道DDR技術。它完全解決了記憶體頻寬的瓶頸,引爆P4處理器的最大動力。在這裡,我們將對比單通道DDR400、雙通道DDR400以及雙通道DDR333之間的性能。當然,此時的P4處理器運行於800MHz前端匯流排。

?雙通道DDR確實是P4處理器的最佳拍檔,在這種環境下,系統的整體性能得到最佳發揮。如果對比一下各種前端匯流排的P4處理器所需要的頻寬以及各種記憶體模式能夠提供的頻寬,我們也就不難理解出現這一現象的原因了。

| | 前端匯流排頻率/工作頻率 | 最高頻寬 |

| Pentium4 | 400MHz | 3.2GB/s |

| Pentium4 | 533MHz | 4.2GB/s |

| Pentium4 | 800MHz | 6.4GB/s |

| DDR266 | 266MHz | 2.1GB/s |

| 雙通道DDR266 | 266MHz | 4.2GB/s |

| DDR333 | 333MHz | 2.7GB/s |

| 雙通道DDR333 | 333MHz | 5.4GB/s |

| DDR400 | 400MHz | 3.2GB/s |

| 雙通道DDR400 | 400MHz | 6.4GB/s |

由於雙通道DDR400的頻寬是6.4GB/s,正好滿足800MHz前端匯流排的P4處理器,因此表現出最佳的組合。

5.Intel-SiS655

Intel晶片組一直對於記憶體異步相當保守,甚至一直不允許記憶體頻率高於CPU的外頻。不過SiS可並不這樣認為,其高端的SiS655晶片組同樣支持雙通道DDR400,而且能夠以更加靈活的方式進行異步,這意味著即便我們的P4處理器運行於533MHz前端匯流排,也可以在SiS655晶片組上使用DDR400。那么這種異步模式是否有價值呢?測試中,我們選擇了533MHz前端匯流排的P4處理器,分別配合單通道DDR400、單通道DDR333以及雙通道DDR333。

計算

記憶體頻寬計算公式:頻寬=記憶體時鐘頻率×記憶體匯流排位數×倍增係數/8。以DDR400記憶體為例,它的運行頻率為200MHz,數據匯流排位數為64bit,由於上升沿和下降沿都傳輸數據,因此倍增係數為2,此時頻寬為:200×64×2/8=3.2GB/s(如果是兩條記憶體組成的雙通道,那頻寬則為6.4 GB/s)。很明顯,在現有技術水準下,運行頻率很難成倍提升,此時數據匯流排位數與倍增係數是技術突破點。

單通道記憶體節制器一般都是64-bit的,8個二進制位相當於1個位元組,換算成位元組是64/8=8,再乘以記憶體的運行頻率,如果是DDR記憶體就要再乘以2,因為它是以SD記憶體雙倍的速度傳輸數據的,所以:

DDR266,運行頻率為133MHz,頻寬為133×2×64/8 = 2.1GBps (PC2100)

DDR333,運行頻率為166MHz,頻寬為166×2×64/8 = 2.7GBps (PC2700)

DDR400,運行頻率為200MHz,頻寬為200×2×64/8 = 3.2GBps (PC3200)

所謂雙通道DDR,就是晶片組可以在兩個不同的數據通道上分離定址、讀取數據。這兩個相互獨立工作的記憶體通道是依靠於兩個獨立並行工作的、位寬為64-bit的記憶體節制器下,因此使普通的DDR記憶體可以到達128-bit的位寬,因此,記憶體頻寬是單通道的兩倍,因此:

雙通道DDR266的頻寬為133×2×64/8×2 = 4.2GBps

雙通道DDR333的頻寬為166×2×64/8×2 = 5.4GBps

雙通道DDR400的頻寬為200×2×64/8×2 = 6.4GBps

提醒,在顯示卡選購時,不要只看顯存的大小,還要注意顯存位寬這個因素,除非有特殊需求,64bit顯存的顯示卡是不建議遊戲玩家購買的。

在了解一些相關的重要知識之後,我們將通過詳細的測試向大家展示記憶體頻寬的奧秘。對於不同的CPU平台,記憶體頻寬與記憶體延時的搭配上,有很多學問。

記憶體頻寬

記憶體頻寬單說來:1、CPU設定為166MHz外頻(333MHz前端匯流排)、DDR運行於DDR333模式;2、CPU設定為166MHz外頻、DDR運行於DDR400。1模式的方案更好。所以,無論在何種情況下,我們都建議nForce2用戶將"Memory Frequency"設定為"Sync(同步)"。事實上,同樣的情況也出現在ALi MAGiK1和SiS745這兩款晶片組上。相反:DDR333在不同步時,性能反而不如DDR266同步,好在它們的市場份額並不大。

矛盾

熟悉記憶體最佳化的朋友一定知道記憶體延時(CL值)的重要性,然而如今大多數DDR記憶體都難以運行在CL=2的模式下,特別在提高其工作頻率的情況下。很多DDR266記憶體能夠在266MHz下穩定運行於CL=2,也可以在333MHz下穩定運行於CL=2.5,同樣的情況也出現在DDR333記憶體中。這就帶給我們這樣一個矛盾,究竟應該提高記憶體頻率還是縮短記憶體延時。

?為此,分別選擇了AMD和Intel的平台進行測試。為了凸現出記憶體頻寬的重要性,我們特意將CL=2時的記憶體頻率低於CPU外頻,這樣的數據更有評判價值。

從測試結果來看,AthlonXP平台顯然對於記憶體延時更加敏感。對於前端匯流排並不高的AthlonXP平台而言,我們認為DDR333+CL2的性能肯定在DDR400+CL2.5之上,因此建議大家在可能的情況下最佳化CL延時。至於I865PE平台,畢竟Pentium4還是對記憶體頻寬相當饑渴,此時自然應該儘可能地保證記憶體頻率,而犧牲記憶體延時。

比較

| | DDR | DDR 2 |

| 目前最高時鐘頻率(單位MHz) | 533(非標準) | 1066(非標準) |

| 數據頻寬(GB/s) | 4.26GB/s | 8.5GB/s |

| 晶片封裝 | FBGA等 | TSOP Ⅱ |

| 工作電壓 | 2.5V | 1.8V |

| 最高物理Bank | 4 | 8 |

| 最高邏輯Bank | 4 | 8 |

| 數據預取(bit) | 2 | 4 |

通過上面的表格,很明顯,DDR2的工作電壓比DDR低近30%,功耗也能相應下降大約50%了。採用FBGA等CSP方式封裝,減小了模組尺寸,並提高信號完整性,它增加了各模組之間的空氣流動空間因而提高了熱性能和可靠性。綜合來看,更容易達到最高的頻率。廠商等不及動作太慢的JEDEC,自行推出了DDR1066的產品。這種產品單條即有8.5GB/s的頻寬,相當於雙通道DDR 533。

由於核心頻率和外部頻率的倍進關係,而我們又是以外部頻率作為衡量記憶體時鐘頻率的標準,因此同頻DDR 2記憶體和DDR記憶體相比,數據傳輸率是一樣的。

僅僅是頻率上的提升,頂多算個“DDR.改”,談不上“DDR 2”。DDR2的重大改進之處就在於數據預取從DDR的2bit提升為4bit。所謂2bit預取,可以理解為記憶體核心向外部I/O緩衝傳遞一次數據,可供外部I/O傳輸兩次的量。而4bit預取,就是記憶體核心向外部I/O緩衝傳遞一次數據,可供外部I/O傳輸4次的量。

記憶體晶片的頻率也有晶片核心頻率和外部頻率兩種:在DDR時代,這兩個頻率是相同的;但在DDR2時代,核心頻率就變成了外部頻率的一半。這是為什麼呢?因為DDR的2bit預取,核心一次傳輸的數據可供外部I/O緩衝傳輸2次,而數據以DDR方式傳輸,數據傳輸是CLK時鐘的上下沿觸發,因此外部時鐘頻率與核心頻率保持一致。而4bit預取就不一樣了,核心一次傳輸數可供外部I/O緩衝傳輸4次,同樣使DDR方式傳輸,外部頻率也要是核心頻率的兩倍才行。

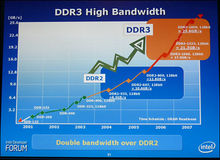

DDR3與DDR2記憶體頻寬比拼

提升頻寬是DDR3記憶體的核心使命

提升頻寬是DDR3記憶體的核心使命提升頻寬是DDR3記憶體的核心使命,這一點無疑是DDR3最為突出的PC使命,簡單地說,DDR3面世就是為了進一步地提升記憶體頻寬,為FSB越來越高的CPU提供足夠的匹配指標。DDR2記憶體其頻率需要可以達到1066MHz這樣的極端頻率,但它的良率及成本都不理想,這種玩家級的產品沒法進入到市場主流。要用低成本切入到更高的頻率的話,新一代的解決方案必將出台,這就是DDR3記憶體了。從技術指標上看,DDR3記憶體的起跑頻率就已經是在1066MHz了,儘管延時參數方面沒法與DDR2記憶體相抗衡,但是將來推出的1600/2000MHz產品的記憶體頻寬肯定大幅度拋離DDR2記憶體,以DDR3 2000MHz為例,其頻寬可以達到16GB/s(雙通道記憶體方案則可以達到32GB/s的理論頻寬值),所以將來DDR3記憶體肯定成為用戶唯一的高頻寬選擇。其實DDR3記憶體提升有效頻率的關鍵依然是舊招數,就是提高預取設計位數,這與DDR2採用的提升頻率的方案是類似的。我們知道,DDR2的預取設計位數是4Bit,也就是說DRAM核心的頻率只有接口頻率的1/4,所以DDR2-800記憶體的核心工作頻率為200MHz的,而DDR3記憶體的預取設計位數提升至8Bit,其DRAM核心的頻率達到了接口頻率的1/8,如此一來同樣運行在200MHz核心工作頻率的DRAM記憶體就可以達到1600MHz的等值頻率,這種“翻倍”的效果在DDR3上依然非常有效。如果說2006年是CPU雙核元年的話,那么2007年則可以說是PC的功耗年,因為2007nian 有太多關係功耗性能比的宣傳,從環保角度去看,降低功耗對業界是有著實實在在的貢獻的,全球的PC每年的耗電量相當驚人,即使是每台PC減低1W的幅度,其省電量都是非常可觀的。DDR3記憶體在達到高頻寬的同時,其功耗反而可以降低,其核心工作電壓從DDR2的1.8V降至1.5V,相關數據預測DDR3將比現時DDR2節省30%的功耗,當然發熱量我們也不需要擔心。就頻寬和功耗之間作個平衡,對比現有的DDR2-800產品,DDR3-800、1066及1333的功耗比分別為0.72X、0.83X及0.95X,不但記憶體頻寬大幅提升,功耗表現也比上代更好。

1、邏輯Bank數量

DDR2 SDRAM中有4Bank和8Bank的設計,目的就是為了應對未來大容量晶片的需求。而DDR3很可能將從2Gb容量起步,因此起始的邏輯Bank就是8個,另外還為未來的16個邏輯Bank做好了準備。

2、封裝(Packages)

DDR3由於新增了一些功能,所以在引腳方面會有所增加,8bit晶片採用78球FBGA封裝,16bit晶片採用96球FBGA封裝,而DDR2則有60/68/84球FBGA封裝三種規格。並且DDR3必須是綠色封裝,不能含有任何有害物質。

3、突髮長度(BL,Burst Length)

由於DDR3的預取為8bit,所以突發傳輸周期(BL,Burst Length)也固定為8,而對於DDR2和早期的DDR架構的系統,BL=4也是常用的,DDR3為此增加了一個4-bit Burst Chop(突發突變)模式,即由一個BL=4的讀取操作加上一個BL=4的寫入操作來合成一個BL=8的數據突發傳輸,屆時可通過A12地址線來控制這一突發模式。而且需要指出的是,任何突發中斷操作都將在DDR3記憶體中予以禁止,且不予支持,取而代之的是更靈活的突發傳輸控制(如4bit順序突發)。

4、定址時序(Timing)

就像DDR2從DDR轉變而來後延遲周期數增加一樣,DDR3的CL周期也將比DDR2有所提高。DDR2的CL範圍一般在2至5之間,而DDR3則在5至11之間,且附加延遲(AL)的設計也有所變化。DDR2時AL的範圍是0至4,而DDR3時AL有三種選項,分別是0、CL-1和CL-2。另外,DDR3還新增加了一個時序參數——寫入延遲(CWD),這一參數將根據具體的工作頻率而定。