基本信息

同或門

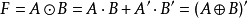

同或門邏輯表達式:(⊙為“同或”運算符)

真值表:

| 輸入A | 輸入B | 輸出F |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

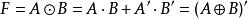

電路中較少使用“同或”門,並且“同或”門可用“異或”門串聯一個“非”門來實現。

實現

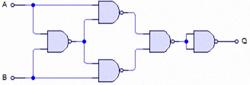

同或門可以只有與非門或者或非門來構成。

同或門 同或門 |  同或門 同或門 |

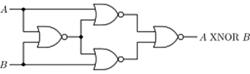

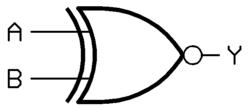

符號

下列包括邏輯門的2種符號:形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標符號(IEC 60617-12)。

ANSI/IEEE Std 91-1984 ANSI/IEEE Std 91-1984 |

積體電路

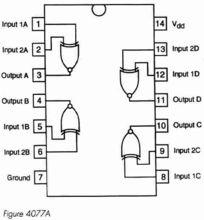

同或門是基本的邏輯門,因此在TTL和CMOS積體電路中都有標準邏輯晶片。標準的4000系列CMOS積體電路為CD4077,包含四個獨立的2輸入同或門。引腳分配如下:

積體電路的引腳分配圖

積體電路的引腳分配圖