介紹

串列/解串器是高速數據通信中的接口電路。串列/解串器在高速數據通信領域已經非常常見,它們不但在光纖數據傳播中起著重要作用,其重要性就如同雙絞線之於網路一樣,在短距離晶片互聯中同樣起著重要作用,能夠有效地減少引腳數和軌跡數(trace count),提高通信數據速率;另一方面,由於提高數據速率能夠對增加對現存資源的利用率(如改善大量光纖基礎設施的數據吞吐量),不斷提高通信中的數據速率已經成為趨勢,於是串列/解串器在如今高速數據通信中扮演著越來越重要的角色。

套用背景

——高速串列數據通信

高速串列數據通信在許多套用中廣泛出現,並且它們在繼續更廣泛的替換掉傳統的並行數據連線系統,例如積體電路設備(IDE)硬碟接口電路、ATA規格或 AT 擴展包接口(ATA/ATAPI),以及雙向並行通信。並行通信和串列通信最基本的差別就在於它們對應的在兩個器件之間用作傳輸數據的物理信道的數量。並行通信意味著數據通路除了連地通路外,還包含有許多物理信道,而串列通信中數據通路常常只存在兩條指定的信道,用於傳輸一對差分信號,同時並不需要連地通路。並行數據通信和串列數據通信的另外一個重要區別,在於二者系統是否工作在同步模式下,並行系統通常工作在同步模式下,串列系統則在非同步模式下,這樣串列系統就允許有一個頻率上的失配,而不需要套用相同的時鐘參考源。

主要結構

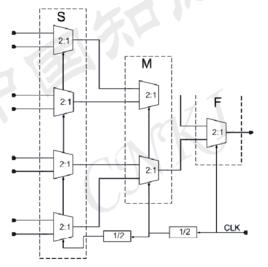

源同步接口

這種結構可以用參考時鐘源來作為捕捉數據的時鐘,也可以由傳送數據端傳送的時鐘來接收數據,所以時鐘數據恢復電路並不是必要的。這種結構可以解決並行連線帶來的兩個主要問題,首先,通過對並行數據進行一定的串化,由n數據位串化為k數據位(k<n),這樣兩晶片之間的信道數減少到k,在接收端,再由k數據位解串為n數據位,減小物理消耗。

串列解串器

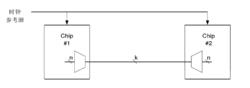

串列解串器前置時鐘

兩晶片之間增加了一條高速時鐘信號通路,時鐘源只需要提供一個較低頻率的時鐘信號,由兩塊晶片內部的鎖相環來倍頻到所需要的時鐘頻率,從而傳送和接收數據。晶片1輸出的時鐘信號,由鎖相環產生,用來傳送數據,同時作為輸出接入到晶片2,被用來捕捉數據,這種改進的結構就叫做前置時鐘結構。

串列解串器

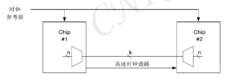

串列解串器差分數據分組

由於接受差分信號的設備決定一個數據位為1還是為0,是根據兩個信號的差,而不是每個信號自己的電平值,所以差分驅動的電路趨向於線性的電流消耗,以及比單端信號產生更小的噪聲。這種採用差分輸出的結構如圖所示,這種結構對於給定的時鐘連線通路,只搭配一定數目的數據信道,能夠有效的增大眼圖的張開度。因為要使眼圖張開度擴大,從時鐘樹到每個數據觸發器和時鐘輸出的通路都應該儘可能的被同樣多的電路所共享,對時鐘的驅動應該等同於對數據的驅動。理想的情況是,一個時鐘驅動器應該驅動時鐘信號到輸出驅動器,同時驅動時鐘輸入到每一個數據觸發器,但是數據匯流排的位數越多,這就越難實現。兩個電路距離越遠,PVT影響就越大,就有越多的電路不能被時鐘分配網路所共享。

串列解串器

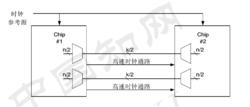

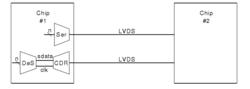

串列解串器目前流行

接收器部分增加了時鐘數據恢復電路(CDR),這樣就使得串列解串器傳送數據時避免了額外傳送高速時鐘信號所帶來的問題,也避免了由於時鐘樹的分配以及PVT對時鐘信號造成的影響,這樣一來僅傳送數據,經過信道的傳輸到達接收器,由接收器的時鐘數據恢復電路對數據進行接收,在數據碼流中恢復出時鐘信號和數據,再將此時鐘信號和數據交給解串器,解串器利用恢復出來的時鐘信號對提取出來的數據進行解串,最終恢復回串列過程之前的並行數據,達到通信功能。許多流行的串列解串器中還包含有前饋均衡器、預加重電路、判決反饋均衡器以及LVDS驅動器等,目的都是使數據眼圖張開度更好。

串列解串器

串列解串器研究現狀

目前國內外的針對於高速串列通信中的串列/解串器商業套用和研究主要呈現出以下兩個特點:首先,產品的IP核化,以前的串列/解串器在市場上流通多是以獨立晶片的形式存在,而如今,更多的出現形式是IP核,因為其作為IP集成在晶片內部,減少了它與相應處理信號模組之間在PCB上的大量線路,大大增強了可復用性並且減小功耗;其次,產品的工作速度越來越高,隨著工藝的逐漸進步,最小線寬逐漸減小,集成度越來越高,處理信號的速度也越來越快,目前的單通道主流產品已經達到了上十Gbps,而相應的研究已經向數十Gbps速率邁進,將多通道的串列/解串器集成在一起,可以極大地提高此接口電路的通信能力,甚至可以達到上百Gbps。