概述

cmos

cmos發展沿革

cmos

cmos在計算機領域,CMOS常指保存計算機基本啟動信息(如日期、時間、啟動設定等)的晶片。有時人們會把CMOS和BIOS混稱,其實CMOS是主機板上的一塊可讀寫的RAM晶片,是用來保存BIOS的硬體配置和用戶對某些參數的設定。CMOS可由主機板的電池供電,即使系統掉電,信息也不會丟失。CMOS RAM本身只是一塊存儲器,只有數據保存功能。而對BIOS中各項參數的設定要通過專門的程式。BIOS設定程式一般都被廠商整合在晶片中,在開機時通過特定的按鍵就可進入BIOS設定程式,方便地對系統進行設定。因此BIOS設定有時也被叫做CMOS設定。

早期的CMOS是一塊單獨的晶片MC146818A(DIP封裝),共有64個位元組存放系統信息。386以後的微機一般將 MC146818A晶片集成到其它的IC晶片中(如82C206,PQFP封裝),586以後主機板上更是將CMOS與系統實時時鐘和後備電池集成到一塊叫做DALLDA DS1287的晶片中。隨著微機的發展、可設定參數的增多,現在的CMOS RAM一般都有128位元組及至256位元組的容量。為保持兼容性,各BIOS廠商都將自己的BIOS中關於CMOS RAM的前64位元組內容的設定統一與MC146818A的CMOS RAM格式一致,而在擴展出來的部分加入自己的特殊設定,所以不同廠家的BIOS晶片一般不能互換,即使是能互換的,互換後也要對CMOS信息重新設定以確保系統正常運行。當今,CMOS製造工藝也被套用於製作數碼影像器材的感光元件,尤其是片幅規格較大的單眼數位相機。雖然在用途上與過去CMOS電路主要作為固件或計算工具的用途非常不同,但基本上它仍然是採取CMOS的工藝,只是將純粹邏輯運算的功能轉變成接收外界光線後轉化為電能,再透過晶片上的數碼─類比轉換器(ADC)將獲得的影像訊號轉變為數位訊號輸出。

優點

相對於其他邏輯系列,CMOS邏輯電路具有一下優點:

1.允許的電源電壓範圍寬,方便電源電路的設計 。

2.邏輯擺幅大,使電路抗干擾能力強。

3.靜態功耗低 ,在獲得相同像素數的情況下,價格更低,具有很高性價比,可以不斷朝更高像素、更高解析度發展。

4.隔離柵結構使CMOS期間的輸入電阻極大,從而使CMOS期間驅動同類邏輯門的能力比其他系列強得多。

套用

cmos

cmos由於CMOS RAM晶片本身只是一塊存儲器,只具有保存數據的功能,所以對CMOS中各項參數的設定要通過專門的程式。早期的CMOS設定程式駐留在軟碟上的(如IBM的PC/AT機型),使用很不方便。現在多數廠家將CMOS設定程式做到了 BIOS晶片中,在開機時通過按下某個特定鍵就可進入CMOS設定程式而非常方便地對系統進行設定,因此這種CMOS設定又通常被叫做BIOS設定。

可讀寫晶片

CMOS是主機板上一塊可讀寫的RAM晶片,用於保存當前系統的硬體配置信息和用戶設定的某些參數。CMOS RAM由主機板上的電池供電,即使系統掉電信息也不會丟失。對CMOS中各項參數的設定和更新可通過開機時特定的按鍵實現(一般是Del鍵)。進入BIOS設定程式可對CMOS進行設定。一般CMOS設定習慣上也被叫做BIOS設定。

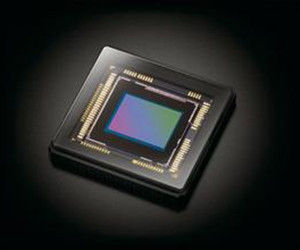

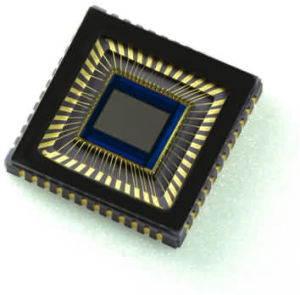

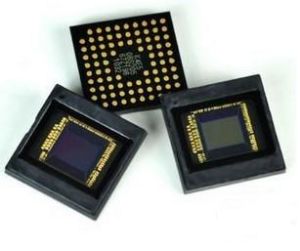

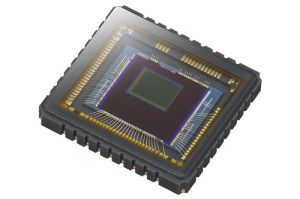

相機領域

CMOS製造工藝也被套用於製作數碼影像器材的感光元件(常見的有TTL和CMOS),尤其是片幅規格較大的單眼數位相機。雖然在用途上與過去CMOS電路主要作為固件或計算工具的用途非常不同,但基本上它仍然是採取CMOS的工藝,只是將純粹邏輯運算的功能轉變成接收外界光線後轉化為電能,再透過晶片上的數碼─類比轉換器(ADC)將獲得的影像訊號轉變為數位訊號輸出。

CMOS與CCD的區別

成像過程

CCD與CMOS圖像感測器光電轉換的原理相同,他們最主要的差別在於信號的讀出過程不同;由於CCD僅有一個(或少數幾個)輸出節點統一讀出,其信號輸出的一致性非常好;而CMOS晶片中,每個像素都有各自的信號放大器,各自進行電荷-電壓的轉換,其信號輸出的一致性較差。但是CCD為了讀出整幅圖像信號,要求輸出放大器的信號頻寬較寬,而在CMOS晶片中,每個像元中的放大器的頻寬要求較低,大大降低了晶片的功耗,這就是CMOS晶片功耗比CCD要低的主要原因。儘管降低了功耗,但是數以百萬的放大器的不一致性卻帶來了更高的固定噪聲,這又是CMOS相對CCD的固有劣勢。

集成性

從製造工藝的角度看,CCD中電路和器件是集成在半導體單晶材料上,工藝較複雜,世界上只有少數幾家廠商能夠生產CCD晶元,如DALSA、SONY、松下等。CCD僅能輸出模擬電信號,需要後續的地址解碼器、模擬轉換器、圖像信號處理器處理,並且還需要提供三組不同電壓的電源同步時鐘控制電路,集成度非常低。而CMOS是集成在被稱作金屬氧化物的半導體材料上,這種工藝與生產數以萬計的計算機晶片和存儲設備等半導體積體電路的工藝相同,因此聲場CMOS的成本相對CCD低很多。同時CMOS晶片能將圖像信號放大器、信號讀取電路、A/D轉換電路、圖像信號處理器及控制器等集成到一塊晶片上,只需一塊晶片就可以實現相機的的所有基本功能,集成度很高,晶片級相機概念就是從這產生的。隨著CMOS成像技術的不斷發展,有越來越多的公司可以提供高品質的CMOS成像晶片,包括:Micron、CMOSIS、Cypress等。

速度

CCD採用逐個光敏輸出,只能按照規定的程式輸出,速度較慢。CMOS有多個電荷-電壓轉換器和行列開關控制,讀出速度快很多,大部分500fps以上的高速相機都是CMOS相機。此外CMOS的地址選通開關可以隨機採樣,實現子視窗輸出,在僅輸出子視窗圖像時可以獲得更高的速度。

噪聲

CCD技術發展較早,比較成熟,採用PN結或二氧化矽(SiO2)隔離層隔離噪聲,成像質量相對CMOS光電感測器有一定優勢。由於CMOS圖像感測器集成度高,各元件、電路之間距離很近,干擾比較嚴重,噪聲對圖像質量影響很大。隨著CMOS電路消噪技術的不斷發展,為生產高密度優質的CMOS圖像感測器提供了良好的條件。

積體電路

cmos

cmosMOS是:金屬-氧化物-半導體(Metal-Oxide-Semiconductor)結構的電晶體簡稱MOS電晶體,有P型MOS管和N型MOS管之分。由MOS管構成的積體電路稱為MOS積體電路,而由PMOS管和NMOS管共同構成的互補型MOS積體電路即為CMOS-IC(ComplementaryMOSIntegratedCircuit)。

數字積體電路按導電類型可分為雙極型積體電路(主要為TTL)和單極型積體電路(CMOS、NMOS、PMOS等)。CMOS電路的單門靜態功耗在毫微瓦(nw)數量級。

電路原理

CMOS由PMOS管和NMOS管共同構成,它的特點是低功耗。由於CMOS中一對MOS組成的門電路在瞬間要么PMOS導通、要么NMOS導通、要么都截至,比線性的三極體(BJT)效率要高得多,因此功耗很低。相對於其他邏輯系列,CMOS邏輯電路具有以下優點:

1、允許的電源電壓範圍寬,方便電源電路的設計

2、邏輯擺幅大,使電路抗干擾能力強

3、靜態功耗低

4、隔離柵結構使CMOS器件的輸入電阻極大,從而使CMOS期間驅動同類邏輯門的能力比其他系列強得多

發展歷史

早期的CMOS元件和主要的競爭對手BJT相比,很容易受到靜電放電(ElectroStaticDischarge,ESD)的破壞。而新一代的CMOS晶片多半在輸出入接腳(I/Opin)和電源及接地端具備ESD保護電路,以避免內部電路元件的閘極或是元件中的PN接面(PN-Junction)被ESD引起的大量電流燒毀。早期的CMOS設定程式駐留在軟碟上的(如IBM的PC/AT機型),使用很不方便。多數廠家將CMOS設定程式做到了BIOS晶片中,在開機時通過按下某個特定鍵就可進入CMOS設定程式而非常方便地對系統進行設定,因此這種CMOS設定又通常被叫做BIOS設定。

CMOS由PMOS管和NMOS管共同構成,它的特點是低功耗。由於CMOS中一對MOS組成的門電路在瞬間要么PMOS導通、要么NMOS導通、要么都截止,比線性的三極體(BJT)效率要高得多,因此功耗很低,因此,計算機里一個紐扣電池就可以給它長時間地提供電力。

優點

相對於其他邏輯系列,CMOS邏輯電路具有以下優點:⒈允許的電源電壓範圍寬,方便電源電路的設計

⒉邏輯擺幅大,使電路抗干擾能力強

⒊靜態功耗低

⒋隔離柵結構使CMOS期間的輸入電阻極大,從而使CMOS期間驅動同類邏輯門的能力比其他系列強得多CMOS發展比TTL晚,但是以其較高的優越性在很多場合逐漸取代了。TTL以下比較兩者性能,大家就知道其原因了。

⒈CMOS是場效應管構成,TTL為雙極電晶體構成

⒉CMOS的邏輯電平範圍比較大(5~15V),TTL只能在5V下工作

⒊CMOS的高低電平之間相差比較大、抗干擾性強,TTL則相差小,抗干擾能力差

⒋CMOS功耗很小,TTL功耗較大(1~5mA/門)

⒌CMOS的工作頻率較TTL略低,但是高速CMOS速度與TTL差不多相當。

詳細信息

1 TTL電平:輸出高電平>2.4V,輸出低電平<0.4V。在室溫下,一般輸出高電平是3.5V,輸出低電平是0.2V。最小輸入高電平和低電平:輸入高電平>=2.0V,輸入低電平<=0.8V,噪聲容限是0.4V。

2 CMOS電平:

邏輯電平電壓接近於電源電壓,0邏輯電平接近於0V。而且具有很寬的噪聲容限。

3 電平轉換電路:

因為TTL和CMOS的高低電平的值不一樣(ttl5v<==>cmos3.3v),所以互相連線時需要電平的轉換:就是用兩個電阻對電平分壓,沒有什麼高深的東西。

4 驅動門電路

OC門,即集電極開路門電路,OD門,即漏極開路門電路,必須外接上拉電阻和電源才能將開關電平作為高低電平用。否則它一般只作為開關大電壓和大電流負載,所以又叫做驅動門電路。

5 TTL和CMOS電路比較:

1)TTL電路是電流控制器件,而CMOS電路是電壓控制器件。

2)TTL電路的速度快,傳輸延遲時間短(5-10ns),但是功耗大。

CMOS電路的速度慢,傳輸延遲時間長(25-50ns),但功耗低。

CMOS電路本身的功耗與輸入信號的脈衝頻率有關,頻率越高,晶片集越熱,這是正常現象。

3)CMOS電路的鎖定效應(擎柱效應):

CMOS電路由於輸入太大的電流,內部的電流急劇增大,除非切斷電源,電流一直在增大。這種效應就是鎖定效應。當產生鎖定效應時,CMOS的內部電流能達到40mA以上,很容易燒毀晶片。

防禦措施1)在輸入端和輸出端加鉗位電路,使輸入和輸出不超過不超過規定電壓。

2)晶片的電源輸入端加去耦電路,防止VDD端出現瞬間的高壓。

3)在VDD和外電源之間加限流電阻,即使有大的電流也不讓它進去。

4)當系統由幾個電源分別供電時,開關要按下列順序:開啟時,先開啟CMOS電路得電源,再開啟輸入信號和負載的電源;關閉時,先關閉輸入信號和負載的電源,再關閉CMOS電路的電源。

6 CMOS電路的使用注意事項

1)CMOS電路時電壓控制器件,它的輸入總抗很大,對干擾信號的捕捉能力很強。所以,不用的管腳不要懸空,要接上拉電阻或者下拉電阻,給它一個恆定的電平。

2)輸入端接低內阻的信號源時,要在輸入端和信號源之間要串聯限流電阻,使輸入的電流限制在1mA之內。

3)當接長信號傳輸線時,在CMOS電路端接匹配電阻。

4)當輸入端接大電容時,應該在輸入端和電容間接保護電阻。電阻值為R=V0/1mA.V0是外界電容上的電壓。

5)CMOS的輸入電流超過1mA,就有可能燒壞CMOS。

7 TTL門電路中輸入端負載特性(輸入端帶電阻特殊情況的處理):

1)懸空時相當於輸入端接高電平。因為這時可以看作是輸入端接一個無窮大的電阻。

2)在門電路輸入端串聯10K電阻後再輸入低電平,輸入端出呈現的是高電平而不是低電平。因為由TTL門電路的輸入端負載特性可知,只有在輸入端接的串聯電阻小於910歐時,它輸入來的低電平信號才能被門電路識別出來,串聯電阻再大的話輸入端就一直呈現高電平。這個一定要注意。CMOS門電路就不用考慮這些了。

8 TTL和CMOS電路的輸出處理

TTL電路有集電極開路OC門,MOS管也有和集電極對應的漏極開路的OD門,它的輸出就叫做開漏輸出。OC門在截止時有漏電流輸出,那就是漏電流,為什麼有漏電流呢?那是因為當三極體截止的時候,它的基極電流約等於0,但是並不是真正的為0,經過三極體的集電極的電流也就不是真正的0,而是約0。而這個就是漏電流。開漏輸出:OC門的輸出就是開漏輸出;OD門的輸出也是開漏輸出。它可以吸收很大的電流,但是不能向外輸出的電流。所以,為了能輸入和輸出電流,它使用的時候要跟電源和上拉電阻一齊用。OD門一般作為輸出緩衝/驅動器、電平轉換器以及滿足吸收大負載電流的需要。

9 什麼叫做圖騰柱,它與開漏電路有什麼區別?

TTL積體電路中,輸出有接上拉三極體的輸出叫做圖騰柱輸出,沒有的叫做OC門。因為TTL就是一個三級關,圖騰柱也就是兩個三級管推挽相連。所以推挽就是圖騰。一般圖騰式輸出,高電平400UA,低電平8MA.

CMOS工藝

製造過程

p肼CMOS工藝

p肼CMOS工藝採用輕摻雜的N型襯底製備PMOS器件。為了做出N型器件,必須先在N型襯底上做出P肼,在p肼內製造NMOS器件。

典型的P肼矽柵CMOS工藝從襯底清洗到中間測試,總共50多道工序,需要5次離子注入,連同刻鈍化視窗,共10次光刻。下面結合主要工藝流程來介紹P肼矽柵CMOS積體電路中元件的形成過程。

⑴光1——光刻肼區,刻出肼區注入孔。

⑵肼區注入及推進,形成肼區。

⑶去除SiO2,長薄氧,長Si3N4

⑷光2——反刻有源區(光刻場區),反刻出P管、N管的源、漏和柵區。

⑸光3——光刻N管場區,刻去N管區上的膠,露出N管場區注入孔。N管場區注入,以提高場開啟,減少閂鎖效應及改善肼的接觸。

⑹長場氧化層,出去Si3N4,再飄去薄的SiO2,然後長柵氧化層。

⑺光4——光刻P管區。p管區注入,調節PMOS管的開啟電壓,然後長多晶矽。

⑻光5——反刻多晶矽,形成多晶矽柵及多晶矽電阻。

⑼光6——光刻P+區,刻去P管及其他P+區上的膠。P+區注入,形成PMOS管的源、漏區及P+保護環。

⑽光7——光刻N+區,刻去N+區上的膠。N+區注入,形成NMOS管的源、漏區及N+保護環。

⑾長PSG

⑿光8——光刻引線孔。可在生長磷矽玻璃後先開一次孔,然後再磷矽玻璃回流及結注入推進後再開第二次孔。

⒀光9——反刻鋁引線。

⒁光10——光刻壓焊塊。

歷史

1963年,快捷半導體的FrankWanlass發明了互補式金屬氧化物半導體電路。到了1968年,美國無線電公司一個由亞伯·梅德溫(AlbertMedwin)領導的研究團隊成功研發出第一個互補式金屬氧化物半導體積體電路。早期的CMOS元件雖然功率消耗比常見的電晶體-電晶體邏輯電路要來得低,但是因為操作速度較慢的緣故,所以大多數套用互補式金屬氧化物半導體的場合都和降低功耗、延長電池使用時間有關,例如電子表。不過經過長期的研究與改良,今日的互補式金屬氧化物半導體元件無論在使用的面積、操作的速度、耗損的功率,以及製造的成本上都比另外一種主流的半導體工藝BJT(BipolarJunctionTransistor,雙載流子電晶體)要有優勢,很多在BJT無法實現或是實作成本太高的設計,利用互補式金屬氧化物半導體皆可順利的完成。只要有任何開發進入到半導體的工藝,往往都可以壓低成本。

早期分離式CMOS邏輯元件只有“4000系列”一種(RCA'COS/MOS'製程),到了後來的“7400系列”時,很多邏輯晶片已經可以利用CMOS、NMOS,甚至是BiCMOS(雙載流子互補式金氧半)製程實現。

早期的CMOS元件和主要的競爭對手BJT相比,很容易受到靜電放電(ElectroStaticDischarge,ESD)的破壞。而新一代的CMOS晶片多半在輸出入接腳(I/Opin)和電源及接地端具備ESD保護電路,以避免內部電路元件的柵極或是元件中的PN結(PN-Junction)被ESD引起的大量電流燒毀。不過大多數晶片製造商仍然會特別警告使用者儘量使用防靜電的措施來避免超過ESD保護電路能處理的能量破壞半導體元件,例如安裝記憶體模組到個人電腦上時,通常會建議使用者配戴防靜電手環之類的設備。

此外,早期的CMOS邏輯元件(如4000系列)的操作範圍可由3伏特至18伏特的直流電壓,所以CMOS元件的柵極使用鋁做為材料。而多年來大多數使用CMOS製造的邏輯晶片也多半在TTL標準規格的5伏特底下操作,直到1990年後,有越來越多低功耗的需求與信號規格出現,取代了雖然有著較簡單的信號接口、但是功耗與速度跟不上時代需求的TTL。此外,隨著MOSFET元件的尺寸越做越小,柵極氧化層的厚度越來越薄,所能承受的柵極電壓也越來越低,有些最新的CMOS製程甚至已經出現低於1伏特的操作電壓。這些改變不但讓CMOS晶片更進一步降低功率消耗,也讓元件的性能越來越好。

近代的CMOS柵極多半使用多晶矽製作。和金屬柵極比起來,多晶矽的優點在於對溫度的忍受範圍較大,使得製造過程中,離子布值(ionimplantation)後的退火(anneal)製程能更加成功。此外,更可以讓在定義柵極區域時使用自我校準(self-align)的方式,這能讓柵極的面積縮小,進一步降低雜散電容(straycapacitance)。2004年後,又有一些新的研究開始使用金屬柵極,不過大部分的製程還是以多晶矽柵極為主。關於柵極結構的改良,還有很多研究集中在使用不同的柵極氧化層材料來取代二氧化矽,例如使用高介電係數介電材料(high-Kdielectric),目的在於降低柵極漏電流(leakagecurrent)。

技術細節

互補式金屬氧化物半導體同時可指互補式金氧半元件及工藝。在同樣的功能需求下,互補式金屬氧化物半導體工藝所製造的積體電路享有功耗較低的優勢,這也使得今日的積體電路產品大多是以互補式金屬氧化物半導體製造。