MOS/CMOS積體電路

MOS積體電路特點:製造工藝比較簡單、成品率較高、功耗低、組成的邏輯電路比較簡單,集成度高、抗干擾能

MOS、CMOS積體電路

MOS、CMOS積體電路MOS積體電路包括:NMOS管組成的NMOS電路、PMOS管組成的PMOS電路及由NMOS和PMOS兩種管子組成的互補MOS電路,即CMOS電路。

PMOS門電路與NMOS電路的原理完全相同,只是電源極性相反而已。

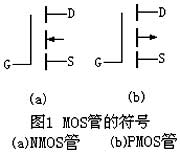

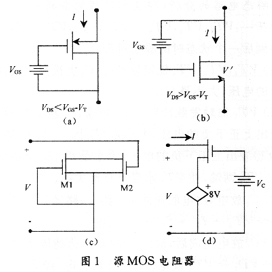

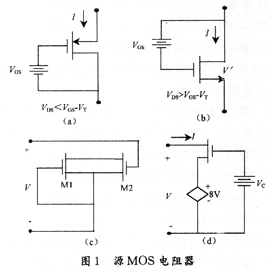

數字電路中MOS積體電路所使用的MOS管均為增強型管子,負載常用MOS管作為有源負載,這樣不僅節省了矽片面積,而且簡化了工藝利於大規模集成。常用的符號如圖1所示。

CMOS積體電路的性能及特點

(1)功耗低

CMOS積體電路採用場效應管,且都是互補結構,工作時兩個串聯的場效應管總是處於一個管導通,另一個管截止的狀態,電路靜態功耗理論上為零。實際上,由於存在漏電流,CMOS電路尚有微量靜態功耗。單個門電路的功耗典型值僅為20mW,動態功耗(在1MHz工作頻率時)也僅為幾mW。

(2)工作電壓範圍寬

CMOS積體電路供電簡單,供電電源體積小,基本上不需穩壓。國產CC4000系列的積體電路,可在3~18V電壓下正常工作。

(3)邏輯擺幅大

MOS、CMOS積體電路

MOS、CMOS積體電路CMOS積體電路的邏輯高電平“1”、邏輯低電平“0”分別接近於電源高電位VDD及電影低電位VSS。當VDD=15V,VSS=0V時,輸出邏輯擺幅近似15V。因此,CMOS積體電路的電壓利用係數在各類積體電路中指標是較高的。

(4)抗干擾能力強

CMOS積體電路的電壓噪聲容限的典型值為電源電壓的45%,保證值為電源電壓的30%。隨著電源電壓的增加,噪聲容限電壓的絕對值將成比例增加。對於VDD=15V的供電電壓(當VSS=0V時),電路將有7V左右的噪聲容限。

(5)輸入阻抗高

CMOS積體電路的輸入端一般都是由保護二極體和串聯電阻構成的保護網路,故比一般場效應管的輸入電阻稍小,但在正常工作電壓範圍內,這些保護二極體均處於反向偏置狀態,直流輸入阻抗取決於這些二極體的泄露電流,通常情況下,等效輸入阻抗高達103~1011Ω,因此CMOS積體電路幾乎不消耗驅動電路的功率。

(6)溫度穩定性能好

由於CMOS積體電路的功耗很低,內部發熱量少,而且,CMOS電路線路結構和電氣參數都具有對稱性,在溫度環境發生變化時,某些參數能起到自動補償作用,因而CMOS積體電路的溫度特性非常好。一般陶瓷金屬封裝的電路,工作溫度為-55 ~ +125℃;塑膠封裝的電路工作溫度範圍為-45 ~ +85℃。

(7)扇出能力強

扇出能力是用電路輸出端所能帶動的輸入端數來表示的。由於CMOS積體電路的輸入阻抗極高,因此電路的輸出能力受輸入電容的限制,但是,當CMOS積體電路用來驅動同類型,如不考慮速度,一般可以驅動50個以上的輸入端。

(8)抗輻射能力強

CMOS積體電路中的基本器件是MOS電晶體,屬於多數載流子導電器件。各種射線、輻射對其導電性能的影響都有限,因而特別適用於製作航天及核實驗設備。

(9)可控性好

CMOS積體電路輸出波形的上升和下降時間可以控制,其輸出的上升和下降時間的典型值為電路傳輸延遲時間的125%~140%。

(10)接口方便

因為CMOS積體電路的輸入阻抗高和輸出擺幅大,所以易於被其他電路所驅動,也容易驅動其他類型的電路或器件。

CMOS積體電路的工作原理

以CMOS積體電路中的一個最基本電路——反相器(其他複雜的CMOS積體電路大多是由反相器單元組合而成)為例,分析CMOS積體電路的工作過程。

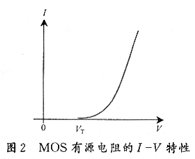

利用一個P溝道MOS管和一個N溝道MOS管互補連線就構成了一個最基本的反相器單元電路如附圖所示。圖2中VDD為正電源端,VSS為負電源端。電路設計採用正邏輯方法,即邏輯“1”為高電平,邏輯“0”為低電平。

圖2中,當輸入電壓VI為低電平“0”(VSS)時,N溝道MOS管的柵-源電壓VGSN=0V(源極和襯底一起接VSS),由於是增強型管,所以管子截止,而P溝道MOS管的柵-源電壓VGSN=VSS—VDD。若|VSS—VDD|>|VTP|(MOS管開啟電壓),則P溝道MOS管導通,所以輸出電壓V0為高電平“1”(VDD),實現了輸入和輸出的反相功能。

當輸入電壓VI為底電平“1”(VDD)時,VGSN=(VDD—VSS)。若(VDD—VSS)>VGSN,則N溝道MOS管導通,此時VGSN=0V,P溝道MOS管截止,所以輸出電壓V0為低電平“0”(VSS),與VI互為反相關係。

由上述分析可知,當輸入信號為“0”或“1”的穩定狀態時,電路中的兩個MOS管總有一個處於截止狀態,使得VDD和VSS之間無低阻抗直流通路,因此靜態功耗極小。這便是CMOS積體電路最主要的特點。

製作CMOS積體電路需要注意的問題

積體電路按電晶體的性質分為TTL和CMOS兩大類,TTL以速度見長,CMOS以功耗低而著稱,其中CMOS電路以其優良的特性成為目前套用最廣泛的積體電路。在電子製作中使用CMOS積體電路時,除了認真閱讀產品說明

MOS、CMOS積體電路

MOS、CMOS積體電路(1)電源問題

1) CMOS積體電路的工作電壓一般在3-18V,但當套用電路中有門電路的模擬套用(如脈衝振盪、線性放大)時,最低電壓則不應低於4.5V。由於CMOS積體電路工作電壓寬,故使用不穩壓的電源電路CMOS積體電路也可以正常工作,但是工作在不同電源電壓的器件,其輸出阻抗、工作速度和功耗是不相同的,在使用中一定要注意。

2)CMOS積體電路的電源電壓必須在規定範圍內,不能超壓,也不能反接。因為在製造過程中,自然形成許多寄生二極體,為反相器電路,在正常電壓下,這些二極體皆處於反偏,對邏輯功能無影響,但是由於這些寄生二極體的存在,一旦電源電壓過高或電壓極性接反,就會使電路產生損壞。

(2)驅動能力問題

CMOS電路的驅動能力的提高,除選用驅動能力較強的緩衝器來完成之外,還可將同一個晶片幾個同類電路並聯起來提高,這時驅動能力提高到N倍(N為並聯門的數量)。

(3)輸入端的問題

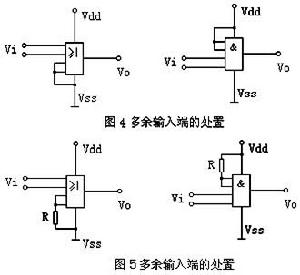

1)多餘輸入端的處理。CMOS電路的輸入端不允許懸空,因為懸空會使電位不定,破壞正常的邏輯關係。另外,懸空時輸入阻抗高,易受外界噪聲干擾,使電路產生誤動作,而且也極易造成柵極感應靜電而擊穿。所以“與”門,“與非”門的多餘輸入端要接高電平,“或”門和“或非”門的多餘輸入端要接低電平。若電路的工作速度不高,功耗也不需特別考慮時,則可以將多餘輸入端與使用端並聯。

2)輸入端接長導線時的保護。在套用中有時輸入端需要接長的導線,而長輸入線必然有較大的分布電容和分布電感,易形成LC振盪,特別當輸入端一旦發生負電壓,極易破壞CMOS中的保護二極體。其保護辦法為在輸入端處接一個電阻, R=VDD/1mA。

3)輸入端的靜電防護。雖然各種CMOS輸入端有抗靜電的保護措施,但仍需小心對待,在存儲和運輸中最好用金屬容器或者導電材料包裝,不要放在易產生靜電高壓的化工材料或化纖織物中。組裝、調試時,工具、儀表、工作檯等均應良好接地。要防止操作人員的靜電干擾造成的損壞,如不宜穿尼龍、化纖衣服,手或工具在接觸集成塊前最好先接一

MOS、CMOS積體電路

MOS、CMOS積體電路4)輸入信號的上升和下降時間不易過長,否則一方面容易造成虛假觸發而導致器件失去正常功能,另一方面還會造成大的損耗。對於74HC系列限於0.5us以內。若不滿足此要求,需用施密特觸發器件進行輸入整形.

5)CMOS電路具有很高的輸入阻抗,致使器件易受外界干擾、衝擊和靜電擊穿,所以為了保護CMOS管的氧化層不被擊穿,一般在其內部輸入端接有二極體保護電路。

其中R約為1.5-2.5KΩ。輸入保護網路的引入使器件的輸入阻抗有一定下降,但仍在108Ω以上。這樣也給電路的套用帶來了一些限制:

①輸入電路的過流保護。CMOS電路輸入端的保護二極體,其導通時電流容限一般為1mA在可能出現過大瞬態輸入電流(超過10mA)時,應串接輸入保護電阻。例如,當輸入端接的信號,其內阻很小、或引線很長、或輸入電容較大時,在接通和關斷電源時,就容易產生較大的瞬態輸入電流,這時必須接輸入保護電阻,若VDD=10V,則取限流電阻為10KΩ即可。

②輸入信號必須在VDD到VSS之間,以防二極體因正向偏置電流過大而燒壞。因此在工作或測試時,必須按照先接通電源後加入信號,先撤除信號後關電源的順序進行操作。在安裝,改變連線,拔插時,必須切斷電源,以防元件受到極大的感應或衝擊而損壞。

③由於保護電路吸收的瞬間能量有限,太大的瞬間信號和過高的靜電電壓將使保護電路失去作用。所以焊接時電烙鐵必須可靠接地,以防漏電擊穿器件輸入端,一般使用時,可斷電後利用電烙鐵的餘熱進行焊接,並先焊其接地管腳。

④要防止用大電阻串入VDD或VSS端,以免在電路開關期間由於電阻上的壓降引起保護二極體瞬時導通而損壞器件。

(4)CMOS的接口電路問題

1)CMOS電路與運放連線。當和運放連線時,若運放採用雙電源,CMOS採用的是獨立的另一組電源,即採用如圖6所示電路,電路中,VD1、VD2為鉗位保護二極體,使CMOS輸入電壓處在10V與地之間。15KΩ的電阻既作為CMOS的限流電阻,又對二極體進行限流保護。若運放使用單電源,且與CMOS使用的電源一樣,則可直接相連。

2)CMOS與TTL等其它電路的連線。在電路中常遇到TTL電路和CMOS電路混合使用的情況,由於這些電路相互之間的電源電壓和輸入、輸出電平及負載能力等參數不同,因此他們之間的連線必須通過電平轉換或電流轉換電路,使前級器件的輸出的邏輯電平滿足後級器件對輸入電平的要求,並不得對器件造成損壞。邏輯器件的接口電路主要應注意電平匹配和輸出能力兩個問題,並與器件的電源電壓結合起來考慮。下面分兩種情況來說明:

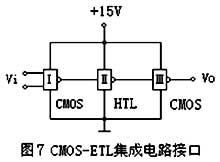

①TTL到CMOS的連線。用TTL電路去驅動CMOS電路時,由於CMOS電路是電壓驅動器件,所需電流小,因此電流驅動能力不會有問題,主要是電壓驅動能力問題,TT L電路輸出高電平的最小值為2.4V,而CMOS電路的輸入高電平一般高於3.5V,這就使二者的邏輯電平不能兼容。為此可採用圖7所示電路,在TTL的輸出端與電源之間接一個電阻R(上拉電阻)可將TTL的電平提高到3.5V以上。 若採用的是OC門驅動,則可採用如圖8所示電路。其中R為其外接電阻。R的取值一般在1-4.7KΩ。

②CMOS到TTL的連線。CMOS電路輸出邏輯電平與TTL電路的輸入電平可以兼容,但CMOS電路的驅動電流較小,不能夠直接驅動TTL電路。為此可採用CMOS/TTL專用接口電路,如CMOS緩衝器CC4049等,經緩衝器之後的高電平輸出電流能滿足TTL電路的要求,低電平輸出電流可達4mA。實現CMOS電路與TTL電路的連線,如圖9所示。 需說明的時,CMOS與TTL電路的接口電路形式多種多樣,實用中應根據具體情況進行選擇。

(5)輸出端的保護問題

1)MOS器件輸出端既不允許和電源短接,也不允許和地短接,否則輸出級的MOS管就會因過流而損壞。

2)在CMOS電路中除了三端輸出器件外,不允許兩個器件輸出端並接,因為不同的器件參數不一致,有可能導致NMOS和PMOS器件同時導通,形成大電流。但為了增加電路的驅動能力,允許把同一晶片上的同類電路並聯使用。 3)當CMOS電路輸出端有較大的容性負載時,流過輸出管的衝擊電流較大,易造成電路失效。為此,必須在輸出端與負載電容間串聯一限流電阻,將瞬態衝擊電流限制在10mA以下。

CMOS積體電路輸入和輸出端使用規則

MOS、CMOS積體電路

MOS、CMOS積體電路在CMOS積體電路的使用中,要求輸入信號幅度不能超過VDD—VSS。輸入信號電流絕對值應小於10mA。如果輸入端接有較大的電容C時,應加保護電阻R,如圖3所示。R的阻值約為幾十歐姆至幾十千歐姆。

(2)多餘輸入端的處置。

CMOS積體電路多餘輸入端的處置比較簡單,下面以或門及與門為例進行說明。如圖4所示,或門(或非門)的多餘輸入端應接至VSS端;與門(與非門)的多餘輸入端應接至VDD端。當電源穩定性差或外界干擾較大時,多餘輸入端一般不直接與電源(地)相連,而是通過一個電阻再與電源(地)相連,如圖5所示,R的阻值約為幾百千歐姆。

另外,採用輸入端並聯的方法來處理多餘的輸入端也是可行的。但這種方法只能在電路工作速度不高,功耗不大的情況下使用。

CMOS積體電路的接口電路

在CMOS積體電路的套用過程中,不可避免地要遇到不同類別的器件間相互連線問題。當各器件的邏輯電平互不一致,不能正確接受和傳遞信息時,要使用接口電路。

MOS、CMOS積體電路

MOS、CMOS積體電路1)CMOS-TTL積體電路的接口

由於TTL的低電平輸入電流1.6mA,而CMOS的低電平輸出電流只有1.5mA,因而一般都得加一個接口電路。這裡介紹一種採用單電源的接口電路。在圖6中,門II起接口電路的作用,是CMOS積體電路緩衝/電平變換器,起緩衝驅動或邏輯電平變換的作用,具有較強的吸收電流的能力,可直接驅動TTL積體電路,因而連線簡便。但是,使用時需要注意相位問題。電路中CC4049是六反相緩衝/變換器,而CC4050是六同相緩衝/變換器。

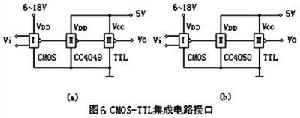

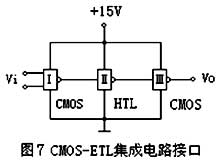

2)CMOS-HTL積體電路的接口

HTL積體電路是標準的工業積體電路,具有較高的抗干擾性能。由於CMOS積體電路的工作電壓很寬,因而可與HTL積體電路共用+15V電源。此時,兩者之間的VOH、VOL及IIH、IIL均互相滿足,不必另設接口電路,直接相連即可,連線電路見圖7。

MOS、CMOS積體電路

MOS、CMOS積體電路3)CMOS-ECL積體電路的接口

ECL積體電路是一種非飽和型的數字邏輯電路。其工作速度居所有邏輯電路之首。ECL採用負電源供電。CMOS積體電路驅動ECL積體電路可使用單電源工作,如圖8所示。ECL積體電路加-5.2V工作電壓,CMOS的VDD接地,VSS接至-5.2V。以ECL積體電路CE10102為例,(CE10102內部包括4個2輸入或非門),流入ECL的輸入高電平電流IIH為265uA,輸入高電平電壓VIH為-1.105V, 在單電源下CMOS電路可以滿足ECL積體電路的輸入需要。

正確使用CMOS、NMOS器件需遵守的準則

MOS、CMOS積體電路

MOS、CMOS積體電路由於不可避免的短時間操作引起的高靜電電壓放電現像,例如人在打臘地板上走動時會引起高達4KV~15KV的靜電高壓,此高壓與環境濕度和表面的條件有關,因而在使用CMOS、NMOS器件時必須遵守下列預防準則:

(1)不要超過手冊上所列出的極限工作條件的限制。

(2)器件上所有空閒的輸入端必須接 VDD 或 VSS,並且要接觸良好。

(3)所有低阻抗設備(例如脈衝信號發生器等)在接到 CMOS 或 NMOS積體電路輸入端以前必然讓器件先接通電源,同樣設備與器件斷開後器件才能斷開電源。

(4)包含有 CMOS 和 NMOS 積體電路的印刷電路板僅僅是一個器件的延伸,同樣需要遵守操作準則。從印刷電路板邊緣的接外掛程式直接聯線到器件也能引起器件損傷,必須避免一般的塑膠包裝,印刷電路板接外掛程式上的 CMOS 或 NMOS 積體電路的地址輸入端或輸出端應當串聯一個電阻,由於這些串聯電阻和輸入電容的時間常數增加了延遲時間。這個電阻將會限制由於印刷電路板移動或與易產生靜電的材料接觸所產生的靜電高壓損傷。

(5)所有 CMOS 和 NMOS 積體電路的儲存和運輸過程必須採用抗靜電材料做成的容器,而不能按常規將器件插入塑膠或放在普通塑膠的托盤內,直到準備使用時才能從抗靜電材料容器中取出來。

(6)所有 CMOS 和 NMOS 積體電路應當放置在接地良好的工作檯上,鑒於工作人員也能對工作檯產出靜電放電,所以工作人員在操作器件之前自身必須先接地,為此建議工作人員要用牢固的導電帶將手腕或肘部與工作台表面連線良好。

(7)尼龍或其它易產生靜電的材料不允許與 CMOS 和 NMOS 積體電路接觸。

MOS、CMOS積體電路

MOS、CMOS積體電路(9)冷凍室要用二氧化碳製冷,並且要放置隔板,而器件必須放在導電材料的容器內。

(10)需要扳直外引線和用手工焊接時,要採用手腕接地的措施,焊料罐也要接地。

(11)波峰焊時要採用下面措施:

a、波峰焊機的焊料罐和傳送帶系統必須接真地。

b、工作檯採用導電的頂蓋遮蓋,要接真地。

c、工作人員必須按照預防準則執行。

d、完成的工件要放到抗靜電容器中,優先送到下一道工序去。

(12)清洗印刷電路板要採用下列措施:

a、蒸氣去油劑和籃筐必須接真地,工作人員同樣要接地。

b、不準使用刷子和噴霧器清洗印數電路板。

c、從清洗籃中拿出來的工件要立即放入蒸汽去油劑中。

d、只有在工件接地良好或在工件上採用靜電消除器後才允許使用高速空氣和溶劑。

(13)必須有生產線監督者的允許才能使用靜電監測儀。

(14)在通電狀態時不準插入或拔出積體電路,絕對應當按下列程式操作:

a、插上積體電路或印刷電路板後才通電。

b、斷電後才能拔出積體電路或印刷電路板。

(15)告誡使用 MOS 積體電路的人員,決不能讓操作人員直接與電氣地相連,為了安全的原因,操作人員與地氣之間的電阻至少應有 100K。

(16)操作人員使用棉織品手套而不要用尼龍手套或橡膠手套。

(17)在工作區,禁止使用地毯。

(18)除非絕對必要外,都不準工作人員觸摸CMOS或NMOS器件的引線端子。