信號調製

基本原理

原理圖

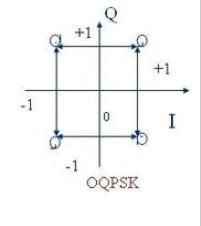

原理圖QPSK調製由於同相支路I和正交支路Q的兩個比特ab可能同時發生變化,因而存在180°的相位突變,這在頻帶受限的系統中會引起信號包絡的很大起伏,造成鄰道干擾。OQPSK調製對此作了改進,它將Q支路的符號在時間上錯開Tb,這樣上下兩個支路的相鄰碼元不可能同時變化,使得相鄰碼元相位差最大縮小至90°,從而減小了信號包絡的起伏。

硬體選擇

OQPSK調製器的硬體開發平台採用的是合眾達的SEED-DEC5416嵌入式DSP開發板,其系統結構原理如圖2所示。處理器是16bit定點DSP晶片TMS320VC5416,OQPSK信號的16位各樣點數據送往轉換精度只有14位的D/A轉換控制器TLC32044,該控制器只對16位中的高14位數據進行D/A轉換,轉換後的波形送示波器顯示。

軟體設計

主程式中首先對TLC32044晶片初始化(過程請查閱相應的PDF資料),然後調用執行OQPSK調製子程式。本文設計的在DSP處理器上實現OQPSK調製的方法。

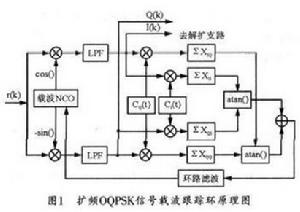

信號解調

硬體電路

vhdl硬體設計

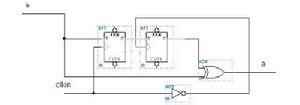

vhdl硬體設計具體電路如圖5所示:其中b為相對碼,a為絕對碼,clkin為為同步信號時鐘。

建模思想

首先判斷前面已存在非0符號的極性,用以判斷後面非0符號的極性。同時通過變數flag的狀態判斷前面是否已經插V,若已經插V則再通過變數H的狀態判斷兩個V之間的非0符號的個數,為偶數且後面連續輸入4個以上連0時則插B,為奇數時則不插B。若尚未插V則不補B。插V和插B的功能由兩個3位移位暫存器的強制輸出實現,當不需要插V和B的時候則移位暫存器順序輸出。

本設計在實現過程中將插入的V和B根據需要直接由+1和-1表示,省去了其他程式中先插入V和B然後再判斷極性的過程。輸出部分由兩路表示,當aout和bout分別為0和1時表示輸出-1,為1和0時表示輸出+1,為0和0時表示輸出0。

隨著FPGA技術的發展,大規模FPGA的容量在不斷增大,價格不斷下降,這使得集成複雜的算法成為可能。用它將實現連續相位OQPSK解調所需的大部分功能封裝於其中,將有利於通信系統實現小型化和集成化,並可提高系統的穩定性。另外,由於FPGA器件具有可程式性,可以很方便地進行系統升級和修改,以滿足不同套用場合的需要。憂無線SOC開發平台豪華的單片機開發系統S3C44B0 ARM7 開發板無憂S3C2410 ARM9開發板單片機乙太網開發板Mini ARM Debugger無憂單片機實驗開發板無憂單片機學習板無線nRF-9E5模組。