概述

DRAM

DRAM在系統內部,RAM是僅次於CPU的最重要的器件之一。它們之間的關係,就如人的大腦中思維與記憶的關係一樣,實際上是密不可分的。但在計算機內部,它們卻是完全獨立的器件,沿著各自的道路向前發展。

第一代個人電腦的CPU8088時鐘頻率還不到10MHZ,而現在高檔的Pentium Pro CPU的時鐘頻率已達到2GHz甚至更高。在CPU和RAM之間有一條高速數據通道,CPU所要處理的數據和指令必須先放到RAM中等待.而CPU也把大部分正在處理的中間數據暫時放置在RAM中,這就要求RAM和CPU之間的速度保持匹配。

原理

DRAM

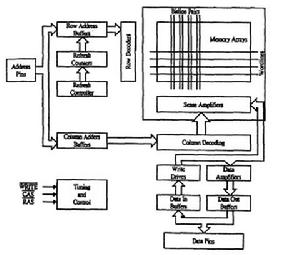

DRAM下圖所示的是標準的DRAM結構的框架圖,和SRAM不同的是,標準DRAM的地址線分成兩組以減少輸入地址引腳的數量,提高封裝的效率。雖然在標準的DRAM結構中,輸入地址引腳的數量可以通過安排多元的地址方式來減少,但是這樣的話,標準DRAM存儲單元的時鐘控制就會變得更加複雜,同時運行速度會受到影響。為了滿足對於高速DRAM套用的需求,一般都用分開的地址輸入引腳來減少時鐘控制的複雜性和提高運行速度。

DRAM的控制器提供行地址選通脈衝-M (Row Address Strobe)和列地址選通脈衝CAS(Column Address Strobe)來鎖定行地址和列地址。正如圖所示,標準DRAM的引腳為:

地址 : 分成兩組,行地址引腳,列地址引腳;

地址控制信號引腳:RAS和CAS;

寫允許信號:WRITE;

數據輸入/輸出引腳;

電源引腳。

結構

DRAM

DRAMDRAM的結構可謂是簡單高效,每一個bit只需要一個電晶體另加一個電容。但是電容不可避免的存在漏電現象,如果電荷不足會導致數據出錯,因此電容必須被周期性的刷新(預充電),這也是DRAM的一大特點。

而且電容的充放電需要一個過程,刷新頻率不可能無限提升(頻障),這就導致DRAM的頻率很容易達到上限,即便有先進工藝的支持也收效甚微。隨著科技的進步,以及人們對超頻的一種意願,這些頻障也在慢慢解決。

改進

“上古”時代的FP/EDO記憶體,由於半導體工藝的限制,頻率只有25MHz/50MHz,自SDR以後頻率從66MHz一路飆升至133MHz,終於遇到了難以逾越的障礙。此後所誕生的DDR1/2/3系列,它們存儲單元官方頻率(JEDEC制定)始終在100MHz-200MHz之間徘徊,非官方(超頻)頻率也頂多在250MHz左右,很難突破300MHz。事實上高頻記憶體的出錯率很高、穩定性也得不到保證,除了超頻跑簡單測試外並無實際套用價值。

既然存儲單元的頻率(簡稱核心頻率,也就是電容的刷新頻率)不能無限提升,那么就只有在I/O(輸入輸出)方面做文章,通過改進I/O單元,這就誕生了DDR1/2/3、GDDR1/2/3/4/5等形形色色的記憶體種類

套用

1.DRAMControllerStatusRegister(Address:0x7E001000)DRAM狀態暫存器,這是一個RO暫存器,用於讀取DRAM的狀態。

實際上,讀到的有用信息就是ControllerStatus和Memorywidth。

2.DRAMControllerCommandRegister(Address:0x7E001004)

DRAM命令暫存器,設定DRAM的工作狀態。

最開始應該配置為0x4,是處於Configure狀態。在配置完所有的DRAM之後,將該暫存器設定為0x0,處於運行狀態。

3.DirectCommandRegister(Address:0x7E001008)

DRAM命令暫存器,用於傳送命令到DRAM和訪問DRAM中的MRS和EMRS暫存器。

通過該暫存器初始化DRAM,先設定為NOP模式,然後設定為PrechargeAll進行充電,然後設定EMRS和MRS暫存器,一般是這么一個流程。具體的要參見你所使用的DRAM的datasheet。

4.MemoryConfigurationRegister(Address:0x7E00100C)

DRAM的配置暫存器,這個與需要參照你所使用的DRAM的datasheet。

該暫存器肯定是要配的,看看DRAM的datasheet就知道了。

術語

1.cache/DRAMcontroller高速緩衝存儲器/動態隨機存取存儲器控制器

2.dynamicrandomaccessmemory(DRAM)

動態隨機存取存儲器

3.memory,dynamicrandomaccess(DRAM)

動態隨機存取存儲器

4.reducedlatencyDRAMRA

時延減少型DRAM

5.RapidLatencyDRAM

快速延遲DRAM