目的

封裝,就是指把矽片上的電路管腳,用導線接引到外部接頭處,以便於其它器件連線。封裝形式是指安裝半導體積體電路晶片用的外殼。它不僅起著安裝、固定、密封、保護晶片及增強電熱性能等方面的作用,而且還通過晶片上的接點用導線連線到封裝外殼的引腳上,這些引腳又通過印刷電路板上的導線與其他器件相連線,從而實現內部晶片與外部電路的連線。因為晶片必須與外界隔離,以防止空氣中的雜質對晶片電路的腐蝕而造成電氣性能下降。另一方面,封裝後的晶片也更便於安裝和運輸。由於封裝技術的好壞還直接影響到晶片自身性能的發揮和與之連線的PCB(印製電路板)的設計和製造,因此它是至關重要的。

衡量一個晶片封裝技術先進與否的重要指標是晶片面積與封裝面積之比,這個比值越接近1越好。

封裝過程

因為從工廠出來的是一塊塊從晶圓上劃下來的矽片,如果不進行封裝,既不方便運輸、保管,也不方便焊接、使用,而且一直暴露在外界會受到空氣中的雜質和水分以及射線的影響,造成損傷從而導致電路失效或性能下降。

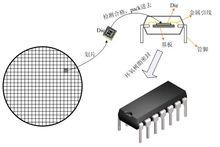

以“雙列直插式封裝”(Dual In-line Package,DIP)為例,下圖簡單示意出其封裝的過程。晶圓上劃出的裸片(Die),經過測試合格後,將其緊貼安放在起承托固定作用的基底上(基底上還有一層散熱良好的材料),再用多根金屬線把Die上的金屬接觸點(Pad,焊盤)跟外部的管腳通過焊接連線起來,然後埋入樹脂,用塑膠管殼密封起來,形成晶片整體。

積體電路封裝示意圖

積體電路封裝示意圖因素

1、 晶片面積與封裝面積之比為提高封裝效率,儘量接近1:1;

2、 引腳要儘量短以減少延遲,引腳間的距離儘量遠,以保證互不干擾,提高性能;

3、 基於散熱的要求,封裝越薄越好。

封裝主要分為DIP雙列直插和SMD貼片封裝兩種。從結構方面,封裝經歷了最早期的電晶體TO(如TO-89、TO92)封裝發展到了雙列直插封裝,隨後由PHILIP公司開發出了SOP小外型封裝,以後逐漸派生出SOJ(J型引腳小外形封裝)、TSOP(薄小外形封裝)、VSOP(甚小外形封裝)、SSOP(縮小型SOP)、TSSOP(薄的縮小型SOP)及SOT(小外形電晶體)、SOIC(小外形積體電路)等。從材料介質方面,包括金屬、陶瓷、塑膠,很多高強度工作條件需求的電路如軍工和宇航級別仍有大量的金屬封裝。

發展進程

結構方面:TO->DIP->PLCC->QFP->BGA->CSP;

材料方面:金屬、陶瓷->陶瓷、塑膠->塑膠;

引腳形狀:長引線直插->短引線或無引線貼裝->球狀凸點;

裝配方式:通孔插裝->表面組裝->直接安裝

具體形式

封裝形式(1—5)

1、BGA(ball grid array)

球形觸點陣列,表面貼裝型封裝之一。在印刷基板的背面按陳列方式製作出球形凸點用以

代替引腳,在印刷基板的正面裝配LSI 晶片,然後用模壓樹脂或灌封方法進行密封。也稱為凸

點陳列載體(PAC)。引腳可超過200,是多引腳LSI 用的一種封裝。

封裝本體也可做得比QFP(四側引腳扁平封裝)小。例如,引腳中心距為1.5mm 的360 引腳

BGA 僅為31mm 見方;而引腳中心距為0.5mm 的304 引腳QFP 為40mm 見方。而且BGA 不

用擔心QFP 那樣的引腳變形問題。

該封裝是美國Motorola 公司開發的,首先在攜帶型電話等設備中被採用,今後在美國有可

能在個人計算機中普及。最初,BGA 的引腳(凸點)中心距為1.5mm,引腳數為225。也有

一些LSI 廠家正在開發500 引腳的BGA。

BGA 的問題是回流焊後的外觀檢查。不清楚是否有效的外觀檢查方法。有的認為,

由於焊接的中心距較大,連線可以看作是穩定的,只能通過功能檢查來處理。

美國Motorola 公司把用模壓樹脂密封的封裝稱為OMPAC,而把灌封方法密封的封裝稱為

GPAC(見OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)

帶緩衝墊的四側引腳扁平封裝。QFP 封裝之一,在封裝本體的四個角設定突起(緩衝墊)以

防止在運送過程中引腳發生彎曲變形。美國半導體廠家主要在微處理器和ASIC 等電路中採用

此封裝。引腳中心距0.635mm,引腳數從84 到196 左右(見QFP)。

3、碰焊PGA(butt joint pin grid array)

表面貼裝型PGA 的別稱(見表面貼裝型PGA)。

4、C-(ceramic)

表示陶瓷封裝的記號。例如,CDIP 表示的是陶瓷DIP。是在實際中經常使用的記號。

5、Cerdip

用玻璃密封的陶瓷雙列直插式封裝,用於ECL RAM,DSP(數位訊號處理器)等電路。帶有

玻璃視窗的Cerdip 用於紫外線擦除型EPROM 以及內部帶有EPROM 的微機電路等。引腳中心

距2.54mm,引腳數從8 到42。在日本,此封裝表示為DIP-G(G 即玻璃密封的意思)。

封裝形式(6—10)

6、Cerquad

表面貼裝型封裝之一,即用下密封的陶瓷QFP,用於封裝DSP 等的邏輯LSI 電路。帶有窗

口的Cerquad 用於封裝EPROM 電路。散熱性比塑膠QFP 好,在自然空冷條件下可容許1.5~

2W 的功率。但封裝成本比塑膠QFP 高3~5 倍。引腳中心距有1.27mm、0.8mm、0.65mm、0.5mm、

0.4mm 等多種規格。引腳數從32 到368。

7、CLCC(ceramic leaded chip carrier)

帶引腳的陶瓷晶片載體,表面貼裝型封裝之一,引腳從封裝的四個側面引出,呈丁字形。

帶有視窗的用於封裝紫外線擦除型EPROM 以及帶有EPROM 的微機電路等。此封裝也稱為

QFJ、QFJ-G(見QFJ)。

8、COB(chip on board)

板上晶片封裝,是裸晶片貼裝技術之一,半導體晶片交接貼裝在印刷線路板上,晶片與基

板的電氣連線用引線縫合方法實現,晶片與基板的電氣連線用引線縫合方法實現,並用樹脂覆

蓋以確保可靠性。雖然COB 是最簡單的裸晶片貼裝技術,但它的封裝密度遠不如TAB 和倒片

焊技術。

9、DFP(dual flat package)

雙側引腳扁平封裝。是SOP 的別稱(見SOP)。以前曾有此稱法,已基本上不用。

10、DIC(dual in-line ceramic package)

陶瓷DIP(含玻璃密封)的別稱(見DIP).

封裝形式(11—15)

11、DIL(dual in-line)

DIP 的別稱(見DIP)。歐洲半導體廠家多用此名稱。

12、DIP(dual in-line package)

雙列直插式封裝。插裝型封裝之一,引腳從封裝兩側引出,封裝材料有塑膠和陶瓷兩種。

DIP 是最普及的插裝型封裝,套用範圍包括標準邏輯IC,存貯器LSI,微機電路等。

引腳中心距2.54mm,引腳數從6 到64。封裝寬度通常為15.2mm。有的把寬度為7.52mm

和10.16mm 的封裝分別稱為skinny DIP 和slim DIP(窄體型DIP)。但多數情況下並不加區分,

只簡單地統稱為DIP。另外,用低熔點玻璃密封的陶瓷DIP 也稱為cerdip(見cerdip)。

13、DSO(dual small out-lint)

雙側引腳小外形封裝。SOP 的別稱(見SOP)。部分半導體廠家採用此名稱。

14、DICP(dual tape carrier package)

雙側引腳帶載封裝。TCP(帶載封裝)之一。引腳製作在絕緣帶上並從封裝兩側引出。由於利

用的是TAB(自動帶載焊接)技術,封裝外形非常薄。常用於液晶顯示驅動LSI,但多數為定製品。

另外,0.5mm 厚的存儲器LSI 簿形封裝正處於開發階段。在日本,按照EIAJ(日本電子機械工

業)會標準規定,將DICP 命名為DTP。

15、DIP(dual tape carrier package)

同上。日本電子機械工業會標準對DTCP 的命名(見DTCP)。

封裝形式(16—20)

16、FP(flat package)

扁平封裝。表面貼裝型封裝之一。QFP 或SOP(見QFP 和SOP)的別稱。部分半導體廠家采

用此名稱。

17、flip-chip

倒焊晶片。裸晶片封裝技術之一,在LSI 晶片的電極區製作好金屬凸點,然後把金屬凸點

與印刷基板上的電極區進行壓焊連線。封裝的占有面積基本上與晶片尺寸相同。是所有封裝技

術中體積最小、最薄的一種。

但如果基板的熱膨脹係數與LSI 晶片不同,就會在接合處產生反應,從而影響連線的可靠

性。因此必須用樹脂來加固LSI 晶片,並使用熱膨脹係數基本相同的基板材料。

18、FQFP(fine pitch quad flat package)

小引腳中心距QFP。通常指引腳中心距小於0.65mm 的QFP(見QFP)。部分導導體廠家采

用此名稱。

19、CPAC(globe top pad array carrier)

美國Motorola 公司對BGA 的別稱(見BGA)。

20、CQFP(quad fiat package with guard ring)

帶保護環的四側引腳扁平封裝。塑膠QFP 之一,引腳用樹脂保護環掩蔽,以防止彎曲變形。

在把LSI 組裝在印刷基板上之前,從保護環處切斷引腳並使其成為海鷗翼狀(L 形狀)。這種封裝

在美國Motorola 公司已批量生產。引腳中心距0.5mm,引腳數最多為208 左右。

封裝形式(21—25)

21、H-(with heat sink)

表示帶散熱器的標記。例如,HSOP 表示帶散熱器的SOP。

22、pin grid array(surface mount type)

表面貼裝型PGA。通常PGA 為插裝型封裝,引腳長約3.4mm。表面貼裝型PGA 在封裝的

底面有陳列狀的引腳,其長度從1.5mm 到2.0mm。貼裝採用與印刷基板碰焊的方法,因而也稱

為碰焊PGA。因為引腳中心距只有1.27mm,比插裝型PGA 小一半,所以封裝本體可製作得不

怎么大,而引腳數比插裝型多(250~528),是大規模邏輯LSI 用的封裝。封裝的基材有多層陶

瓷基板和玻璃環氧樹脂印刷基數。以多層陶瓷基材製作封裝已經實用化。

23、JLCC(J-leaded chip carrier)

J 形引腳晶片載體。指帶視窗CLCC和帶視窗的陶瓷QFJ 的別稱(見CLCC 和QFJ)。部分半

導體廠家採用的名稱。

24、LCC(Leadless chip carrier)

無引腳晶片載體。指陶瓷基板的四個側面只有電極接觸而無引腳的表面貼裝型封裝。是高

速和高頻IC 用封裝,也稱為陶瓷QFN 或QFN-C(見QFN)。

25、LGA(land grid array)

觸點陳列封裝。即在底面製作有陣列狀態坦電極觸點的封裝。裝配時插入插座即可。現已

實用的有227 觸點(1.27mm 中心距)和447 觸點(2.54mm 中心距)的陶瓷LGA,套用於高速邏輯

LSI 電路。

LGA 與QFP 相比,能夠以比較小的封裝容納更多的輸入輸出引腳。另外,由於引線的阻抗

小,對於高速LSI 是很適用的。但由於插座製作複雜,成本高,基本上不怎么使用。預計

今後對其需求會有所增加。

封裝形式(26—30)

26、LOC(lead on chip)

晶片上引線封裝。LSI封裝技術之一,引線框架的前端處於晶片上方的一種結構,晶片的

中心附近製作有凸焊點,用引線縫合進行電氣連線。與原來把引線框架布置在晶片側面附近的

結構相比,在相同大小的封裝中容納的晶片達1mm 左右寬度。

27、LQFP(low profile quad flat package)

薄型QFP。指封裝本體厚度為1.4mm 的QFP,是日本電子機械工業會根據制定的新QFP

外形規格所用的名稱。

28、L-QUAD

陶瓷QFP 之一。封裝基板用氮化鋁,基導熱率比氧化鋁高7~8 倍,具有較好的散熱性。

封裝的框架用氧化鋁,晶片用灌封法密封,從而抑制了成本。是為邏輯LSI 開發的一種封裝,

在自然空冷條件下可容許W3的功率。現已開發出了208引腳(0.5mm 中心距)和160 引腳(0.65mm

中心距)的LSI 邏輯用封裝,並於1993 年10 月開始投入批量生產。

29、MCM(multi-chip module)

多晶片組件。將多塊半導體裸晶片組裝在一塊布線基板上的一種封裝。根據基板材料可分

為MCM-L,MCM-C 和MCM-D 三大類。

MCM-L 是使用通常的玻璃環氧樹脂多層印刷基板的組件。布線密度不怎么高,成本較低。

MCM-C 是用厚膜技術形成多層布線,以陶瓷(氧化鋁或玻璃陶瓷)作為基板的組件,與使

用多層陶瓷基板的厚膜混合IC 類似。兩者無明顯差別。布線密度高於MCM-L。

MCM-D 是用薄膜技術形成多層布線,以陶瓷(氧化鋁或氮化鋁)或Si、Al 作為基板的組件。

布線密謀在三種組件中是最高的,但成本也高。

30、MFP(mini flat package)

小形扁平封裝。塑膠SOP 或SSOP 的別稱(見SOP 和SSOP)。部分半導體廠家採用的名稱。

封裝形式(31—35)

31、MQFP(metric quad flat package)

按照JEDEC(美國聯合電子設備委員會)標準對QFP 進行的一種分類。指引腳中心距為

0.65mm、本體厚度為3.8mm~2.0mm 的標準QFP(見QFP)。

32、MQUAD(metal quad)

美國Olin 公司開發的一種QFP 封裝。基板與封蓋均採用鋁材,用粘合劑密封。在自然空冷

條件下可容許2.5W~2.8W 的功率。日本新光電氣工業公司於1993 年獲得特許開始生產。

33、MSP(mini square package)

QFI 的別稱(見QFI),在開發初期多稱為MSP。QFI 是日本電子機械工業會規定的名稱。

34、OPMAC(over molded pad array carrier)

模壓樹脂密封凸點陳列載體。美國Motorola 公司對模壓樹脂密封BGA 採用的名稱(見

BGA)。

35、P-(plastic)

表示塑膠封裝的記號。如PDIP 表示塑膠DIP。

封裝形式(36—40)

36、PAC(pad array carrier)

凸點陳列載體,BGA 的別稱(見BGA)。

37、PCLP(printed circuit board leadless package)

印刷電路板無引線封裝。日本富士通公司對塑膠QFN(塑膠LCC)採用的名稱(見QFN)。引

腳中心距有0.55mm 和0.4mm 兩種規格。正處於開發階段。

38、PFPF(plastic flat package)

塑膠扁平封裝。塑膠QFP 的別稱(見QFP)。部分LSI 廠家採用的名稱。

39、PGA(pin grid array)

陳列引腳封裝。插裝型封裝之一,其底面的垂直引腳呈陳列狀排列。封裝基材基本上都采

用多層陶瓷基板。在未專門表示出材料名稱的情況下,多數為陶瓷PGA,用於高速大規模邏輯

LSI 電路。成本較高。引腳中心距通常為2.54mm,引腳數從64 到447 左右。

了為降低成本,封裝基材可用玻璃環氧樹脂印刷基板代替。也有64~256 引腳的塑膠PGA。

另外,還有一種引腳中心距為1.27mm 的短引腳表面貼裝型PGA(碰焊PGA)。(見表面貼裝

型PGA)。

40、piggy back

馱載封裝。指配有插座的陶瓷封裝,形關與DIP、QFP、QFN 相似。在開發帶有微機的設

備時用於評價程式確認操作。例如,將EPROM 插入插座進行調試。這種封裝基本上都是定製

品,市場上不怎么流通。

封裝形式(41—45)

41、PLCC(plastic leaded chip carrier)

帶引線的塑膠晶片載體。表面貼裝型封裝之一。引腳從封裝的四個側面引出,呈丁字形,

是塑膠製品。美國德克薩斯儀器公司首先在64k 位DRAM 和256kDRAM 中採用,已經普

及用於邏輯LSI、DLD(或程邏輯器件)等電路。引腳中心距1.27mm,引腳數從18 到84。

J 形引腳不易變形,比QFP 容易操作,但焊接後的外觀檢查較為困難。

PLCC 與LCC(也稱QFN)相似。以前,兩者的區別僅在於前者用塑膠,後者用陶瓷。但現

在已經出現用陶瓷製作的J 形引腳封裝和用塑膠製作的無引腳封裝(標記為塑膠LCC、PCLP、P

-LCC 等),已經無法分辨。為此,日本電子機械工業會於1988 年決定,把從四側引出J 形引

腳的封裝稱為QFJ,把在四側帶有電極凸點的封裝稱為QFN(見QFJ 和QFN)。

42、P-LCC(plastic teadless chip carrier)(plastic leaded chip currier)

有時候是塑膠QFJ 的別稱,有時候是QFN(塑膠LCC)的別稱(見QFJ 和QFN)。部分

LSI 廠家用PLCC 表示帶引線封裝,用P-LCC 表示無引線封裝,以示區別。

43、QFH(quad flat high package)

四側引腳厚體扁平封裝。塑膠QFP 的一種,為了防止封裝本體斷裂,QFP 本體製作得

較厚(見QFP)。部分半導體廠家採用的名稱。

44、QFI(quad flat I-leaded packgac)

四側I 形引腳扁平封裝。表面貼裝型封裝之一。引腳從封裝四個側面引出,向下呈I 字。

也稱為MSP(見MSP)。貼裝與印刷基板進行碰焊連線。由於引腳無突出部分,貼裝占有面積小

於QFP。

日立製作所為視頻模擬IC 開發並使用了這種封裝。此外,日本的Motorola 公司的PLL IC

也採用了此種封裝。引腳中心距1.27mm,引腳數從18 於68。

45、QFJ(quad flat J-leaded package)

四側J 形引腳扁平封裝。表面貼裝封裝之一。引腳從封裝四個側面引出,向下呈J 字形。

是日本電子機械工業會規定的名稱。引腳中心距1.27mm。

材料有塑膠和陶瓷兩種。塑膠QFJ 多數情況稱為PLCC(見PLCC),用於微機、門陳列、

DRAM、ASSP、OTP 等電路。引腳數從18 至84。

陶瓷QFJ 也稱為CLCC、JLCC(見CLCC)。帶視窗的封裝用於紫外線擦除型EPROM 以及

帶有EPROM 的微機晶片電路。引腳數從32 至84。

封裝形式(46—50)

46、QFN(quad flat non-leaded package)

四側無引腳扁平封裝。表面貼裝型封裝之一。多稱為LCC。QFN 是日本電子機械工業

會規定的名稱。封裝四側配置有電極觸點,由於無引腳,貼裝占有面積比QFP 小,高度比QFP

低。但是,當印刷基板與封裝之間產生應力時,在電極接觸處就不能得到緩解。因此電極觸點

難於作到QFP 的引腳那樣多,一般從14 到100 左右。

材料有陶瓷和塑膠兩種。當有LCC 標記時基本上都是陶瓷QFN。電極觸點中心距1.27mm。

塑膠QFN 是以玻璃環氧樹脂印刷基板基材的一種低成本封裝。電極觸點中心距除1.27mm 外,

還有0.65mm 和0.5mm 兩種。這種封裝也稱為塑膠LCC、PCLC、P-LCC 等。

47、QFP(quad flat package)

四側引腳扁平封裝。表面貼裝型封裝之一,引腳從四個側面引出呈海鷗翼(L)型。基材有陶

瓷、金屬和塑膠三種。從數量上看,塑膠封裝占絕大部分。當沒有特別表示出材料時,多數情

況為塑膠QFP。塑膠QFP 是最普及的多引腳LSI 封裝。不僅用於微處理器,門陳列等數字邏輯LSI 電路,而且也用於VTR信號處理、音響信號處理等模擬LSI 電路。引腳中心距有1.0mm、0.8mm、

0.65mm、0.5mm、0.4mm、0.3mm 等多種規格。0.65mm 中心距規格中最多引腳數為304。

日本將引腳中心距小於0.65mm 的QFP 稱為QFP(FP)。但日本電子機械工業會對QFP

的外形規格進行了重新評價。在引腳中心距上不加區別,而是根據封裝本體厚度分為

QFP(2.0mm~3.6mm 厚)、LQFP(1.4mm 厚)和TQFP(1.0mm 厚)三種。

另外,有的LSI 廠家把引腳中心距為0.5mm 的QFP 專門稱為收縮型QFP 或SQFP、VQFP。

但有的廠家把引腳中心距為0.65mm 及0.4mm 的QFP 也稱為SQFP,至使名稱稍有一些混亂。

QFP 的缺點是,當引腳中心距小於0.65mm 時,引腳容易彎曲。為了防止引腳變形,現已

出現了幾種改進的QFP 品種。如封裝的四個角帶有樹指緩衝墊的BQFP(見BQFP);帶樹脂保護

環覆蓋引腳前端的GQFP(見GQFP);在封裝本體裡設定測試凸點、放在防止引腳變形的專用夾

具里就可進行測試的TPQFP(見TPQFP)。

在邏輯LSI 方面,不少開發品和高可靠品都封裝在多層陶瓷QFP 里。引腳中心距最小為

0.4mm、引腳數最多為348 的產品也已問世。此外,也有用玻璃密封的陶瓷QFP(見Gerqad)。

48、QFP(FP)(QFP fine pitch)

小中心距QFP。日本電子機械工業會標準所規定的名稱。指引腳中心距為0.55mm、0.4mm、

0.3mm 等小於0.65mm 的QFP(見QFP)。

49、QIC(quad in-line ceramic package)

陶瓷QFP 的別稱。部分半導體廠家採用的名稱(見QFP、Cerquad)。

50、QIP(quad in-line plastic package)

塑膠QFP 的別稱。部分半導體廠家採用的名稱(見QFP)。

封裝形式(51—55)

51、QTCP(quad tape carrier package)

四側引腳帶載封裝。TCP 封裝之一,在絕緣帶上形成引腳並從封裝四個側面引出。是利用

TAB 技術的薄型封裝(見TAB、TCP)。

52、QTP(quad tape carrier package)

四側引腳帶載封裝。日本電子機械工業會於1993 年4 月對QTCP 所制定的外形規格所用的

名稱(見TCP)。

53、QUIL(quad in-line)

QUIP的別稱(見QUIP)。

54、QUIP(quad in-line package)

四列引腳直插式封裝。引腳從封裝兩個側面引出,每隔一根交錯向下彎曲成四列。引腳中

心距1.27mm,當插入印刷基板時,插入中心距就變成2.5mm。因此可用於標準印刷線路板。是

比標準DIP 更小的一種封裝。日本電氣公司在台式計算機和家電產品等的微機晶片中採用了些

種封裝。材料有陶瓷和塑膠兩種。引腳數64。

55、SDIP (shrink dual in-line package)

收縮型DIP。插裝型封裝之一,形狀與DIP 相同,但引腳中心距(1.778mm)小於DIP(2.54mm),

因而得此稱呼。引腳數從14 到90。也有稱為SH-DIP 的。材料有陶瓷和塑膠兩種。

封裝形式(56—60)

56、SH-DIP(shrink dual in-line package)

同SDIP。部分半導體廠家採用的名稱。

57、SIL(single in-line)

SIP 的別稱(見SIP)。歐洲半導體廠家多採用SIL 這個名稱。

58、SIMM(single in-line memory module)

單列存貯器組件。只在印刷基板的一個側面附近配有電極的存貯器組件。通常指插入插座

的組件。標準SIMM 有中心距為2.54mm 的30 電極和中心距為1.27mm 的72 電極兩種規格。

在印刷基板的單面或雙面裝有用SOJ 封裝的1 兆位及4 兆位DRAM 的SIMM 已經在個人

計算機、工作站等設備中獲得廣泛套用。至少有30~40%的DRAM 都裝配在SIMM 里。

59、SIP(single in-line package)

單列直插式封裝。引腳從封裝一個側面引出,排列成一條直線。當裝配到印刷基板上時封

裝呈側立狀。引腳中心距通常為2.54mm,引腳數從2 至23,多數為定製產品。封裝的形狀各

異。也有的把形狀與ZIP 相同的封裝稱為SIP。

60、SK-DIP(skinny dual in-line package)

DIP 的一種。指寬度為7.62mm、引腳中心距為2.54mm 的窄體DIP。通常統稱為DIP(見

DIP)。

封裝形式(61—65)

61、SL-DIP(slim dual in-line package)

DIP 的一種。指寬度為10.16mm,引腳中心距為2.54mm 的窄體DIP。通常統稱為DIP。

62、SMD(surface mount devices)

表面貼裝器件。偶而,有的半導體廠家把SOP 歸為SMD(見SOP)。

63、SO(small out-line)

SOP 的別稱。世界上很多半導體廠家都採用此別稱。(見SOP)。

64、SOI(small out-line I-leaded package)

I 形引腳小外型封裝。表面貼裝型封裝之一。引腳從封裝雙側引出向下呈I 字形,中心距

1.27mm。貼裝占有面積小於SOP。日立公司在模擬IC(電機驅動用IC)中採用了此封裝。引腳數

26。

65、SOIC(small out-line integrated circuit)

SOP 的別稱(見SOP)。國外有許多半導體廠家採用此名稱。

封裝形式(66—70)

66、SOJ(Small Out-Line J-Leaded Package)

J 形引腳小外型封裝。表面貼裝型封裝之一。引腳從封裝兩側引出向下呈J 字形,故此得名。

通常為塑膠製品,多數用於DRAM 和SRAM 等存儲器LSI 電路,但絕大部分是DRAM。用SOJ

封裝的DRAM 器件很多都裝配在SIMM 上。引腳中心距1.27mm,引腳數從20 至40(見SIMM)。

67、SQL(Small Out-Line L-leaded package)

按照JEDEC(美國聯合電子設備工程委員會)標準對SOP 所採用的名稱(見SOP)。

68、SONF(Small Out-Line Non-Fin)

無散熱片的SOP。與通常的SOP 相同。為了在功率IC 封裝中表示無散熱片的區別,有意

增添了NF(non-fin)標記。部分半導體廠家採用的名稱(見SOP)。

69、SOF(small Out-Line package)

小外形封裝。表面貼裝型封裝之一,引腳從封裝兩側引出呈海鷗翼狀(L 字形)。材料有塑膠

和陶瓷兩種。另外也叫SOL 和DFP。

SOP 除了用於存儲器LSI 外,也廣泛用於規模不太大的ASSP 等電路。在輸入輸出端子不

超過10~40 的領域,SOP 是普及最廣的表面貼裝封裝。引腳中心距1.27mm,引腳數從8~44。

另外,引腳中心距小於1.27mm 的SOP 也稱為SSOP;裝配高度不到1.27mm 的SOP 也稱為

TSOP(見SSOP、TSOP)。還有一種帶有散熱片的SOP。

70、SOW (Small Outline Package(Wide-Type))

寬體SOP。部分半導體廠家採用的名稱。

所謂封裝是指安裝積體電路用的外殼,它不僅起著安放、固定、密封、保護晶片和增強電熱性能的作用,而且還是溝通晶片內部世界與外部電路的橋樑,晶片上的接點用導線連線到封裝外殼的引腳上,這些引腳又通過基板上的導線與其他元器件進行連線。因此,對於很多積體電路產品而言,封裝技術都是非常關鍵的一環,對晶片自身性能的表現和發揮有重要的影響。

按照封裝材料,積體電路的封裝可以分為金屬封裝、塑膠封裝、陶瓷封裝等。其中塑膠封裝的積體電路最常用。

塑膠封裝的積體電路又有方形扁平式和小型外殼式兩大類,前者適用於多引腳電路,後者適用於少引腳電路。

按照封裝外形,積體電路的封裝可以分為直插式封裝、貼片式封裝、BGA封裝等類型。下面介紹幾種常用的積體電路封裝。

1.直插式封裝

直插式封裝積體電路是引腳插入印製板中,然後再焊接的一種積體電路封裝形式,主要有單列式封裝和雙列直插式封裝。其中單列式封裝有單列直插式封裝(Single Inline Package,縮寫為SIP和單列曲插式封裝(Zig-ZagInline Package,縮寫為ZIP),單列直插式封裝的積體電路只有一排引腳,單列曲插式封裝的積體電路一排引腳又分成兩排進行安裝。

雙列直插式封裝又稱D I P封裝(Dual Inline Package),這種封裝的積體電路具有兩排引腳。適合PCB的穿孔安裝;易於對PCB布線;安裝方便。雙列直插式封裝的結構形式主要有多層陶瓷雙列直插式封裝、單層陶瓷雙列直插式封裝、引線框架式封裝等。

2.貼片封裝

隨著生產技術的提高,電子產品的體積越來越小,體積較大的直插式封裝積體電路已經不能滿足需要。故設計者又研製出一種貼片封裝的積體電路,這種封裝的積體電路引腳很小,可以直接焊接在印製電路板的印製導線上。貼片封裝的積體電路主要有薄型Q F P(TQFP)、細引腳間距QFP(VQFP)、縮小型Q F P(S Q F P)、塑膠Q F P(PQFP)、金屬QFP(MetalQFP)、載帶QFP(TapeQFP)、J型引腳小外形封裝(SOJ)、薄小外形封裝(TSOP)、甚小外形封裝(V S O P)、縮小型S OP(SSOP)、薄的縮小型SOP(TSSOP)及小外形積體電路(SOIC)等派生封裝。

3.BGA封裝 (Ball Grid Array Package)

又名球柵陣列封裝,BGA封裝的引腳以圓形或柱狀焊點按陣列形式分布在封裝下面。採用該封裝形式的積體電路主要有CPU以及南北橋等的高密度、高性能、多功能積體電路。

BGA封裝積體電路的優點是雖然增加了引腳數,但引腳間距並沒有減小反而增加了,從而提高了組裝成品率;厚度和重量都較以前的封裝技術有所減少;寄生參數減小,信號傳輸延遲小,使用頻率大大提高;組裝可用共面焊接,可靠性高。

4.厚膜封裝

厚膜積體電路就是把專用的積體電路晶片與相關的電容、電阻元件都集成在一個基板上,然後在其外部採用標準的封裝形式,並引出引腳的一種模組化的積體電路。

FAQ

1.什麼是數據包封裝? 當一個計算機要傳送數據信息給另一個計算機時,得添加一些網路控制信息和數據信息一起傳送,在傳送的過程中,網路設備會根據控制信息而決定如何轉發。網路控制信息的例子包括地址、session ID、協定參數。 添加控制信息的操作就是封裝。 2. 為什麼要封裝數據包? 簡單的答案是:符合OSI模式的要求。 分析這個要求的根源得從網路結構說起:網路的主要功能常能被不同的技術實現,而網路技術更新速度很快,要能允許不同的技術共存而不影響全局,得模組化,把模組間的接口定義好,模組內部的改變就不至於影響到其他模組。OSI模式把網路分為7層,和軟體相關的常用的四層是link, network, transport, protocol (第二、三、四、五層). 每一層的作用、參數被格式化的定義。在發包前,先封裝每一層的控制信息到個別的報頭。在收到數據包時,網路設備可以一層層的解封裝報頭,讀出協定參數、根據協定而做出決定。 換言之,封裝是一種網路模組化的機制,它使得分布各處的網路可以從收到的數據包讀到控制信息,根據協定做出合適的反應。3. 主機是怎么封裝、解封裝數據包的?? 在這個案例中,主機封裝的重點如下:- 協定報頭:設protocol,4. 信息、數據包、報頭的大小關係是什麼?舉例說明:在乙太網中,主機H1要傳送一個3300byte 的 信息給主機H2。由於乙太網限制數據包的長度不能超過1500 byte, 這個信息被分割為三個數據包,每個數據包都有三個報頭,(就是協定是ICMP): packet payload link header IP header ICMP header Subtotal 1 15 300 14 20 8 342 信息是3300 byte, 報頭是 126 byte, 報頭占3%: 126/(3300+126)=3%. 報頭並沒有耗費過多的網路頻寬資源。

![封裝[電路集成術語] 封裝[電路集成術語]](/img/1/c43/nBnauM3XyYjN4YTNxMzN1ATN0UTMyITNykTO0EDMwAjMwUzLzczLwQzLt92YucmbvRWdo5Cd0FmLwE2LvoDc0RHa.jpg)