基本解釋

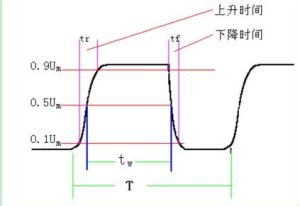

數字電路中,把電壓的高低用邏輯電平來表示。邏輯電平包括高電平和低電平這兩種。不同的元器件形成的數字電路,電壓對應的邏輯電平也不同。在TTL門電路中,把大於3.5伏的電壓規定為邏輯高電平,用數字1表示;把電壓小於0.3伏的電壓規定為邏輯低電平,用數字0表示。數字電平從低電平(數字“0”)變為高電平(數字“1”)的那一瞬間(時刻)叫作上升沿。

硬體描述語言

在Verilog等硬體描述語言中,用“posedge”表示“上升沿”。

套用示例

上升沿可以被用來觸發時序控制,在時間脈衝上升沿觸發的T觸發器就是一個典型的例子,這類觸發器並不是通常的電平敏感,而是信號邊緣敏感。